迂回曲折:Maxim Integrated 通过双核 Arm/RISC-V 微控制器消除了 RISC-V 的风险

尽管 Arm 内核已被证明是成熟可靠的,且目前已用于大多的移动设备和物联网 (IoT) 端点,但是如果有替代备用方案总是有用和保险的,毕竟一药不能包治百病。

现在我们来谈谈 RISC-V 32 位 CPU。RISC-V(读作“risk-five”)是一种开源的非专利架构,对于在很长时间以来一直占主导地位的 Arm CPU 内核生态系统来说,它是第一个能威胁其地位的架构。基本 RV32 变型具有 31 个通用 32 位寄存器,命名为 x1 至 x31(寄存器 x0 硬接线到 0)。它支持架构扩展,可针对不同应用灵活使用。例如,当构建微控制器时,“B” RISC-V 扩展支持原生位操作,从本人在微控制器方面的长期经验来看,这表示该架构很适合深度嵌入。

正是这种深度嵌入挑战不断让工程师们接受新的架构。面对现有的采购潮流时,如果您逆流而行,适应过程必将安绊不断。

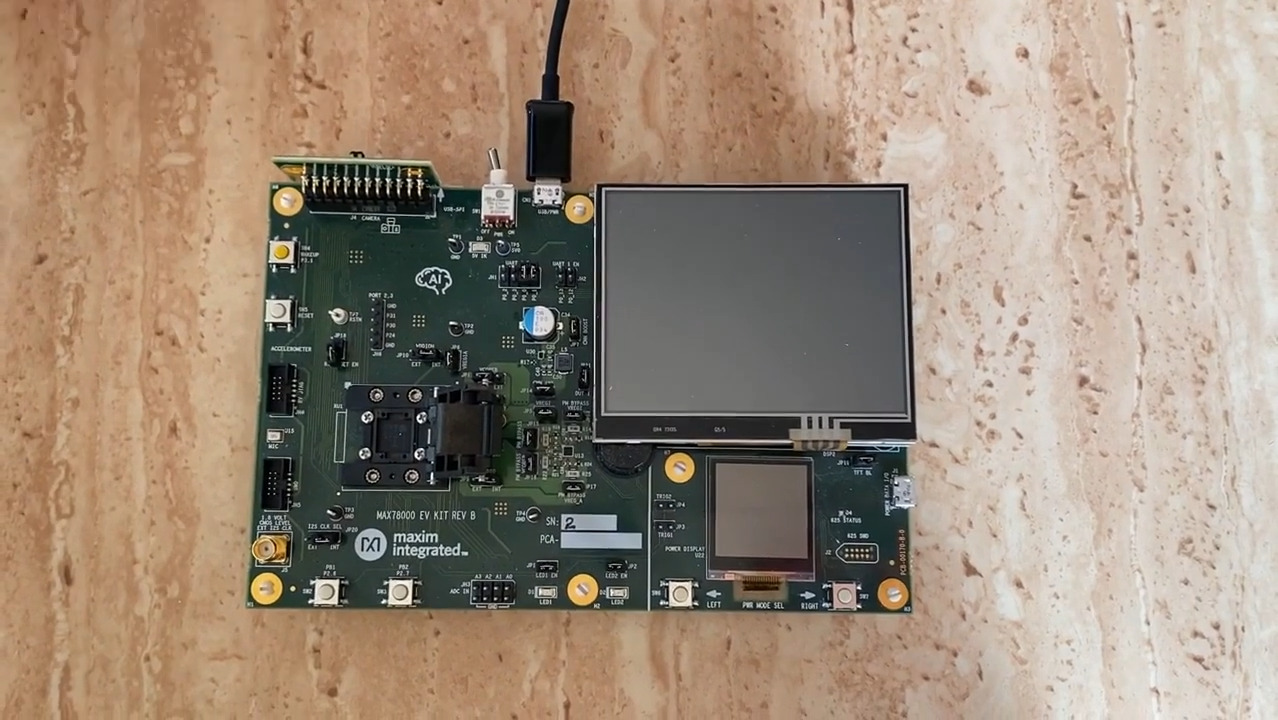

Maxim Integrated 通过顺应这种采购潮流,解决了这种适应性问题。MAX78000EXG+ 是一个双核微控制器,采用 100 兆赫 (MHz) Arm Cortex-M4 内核,带有浮点单元 (FPU) 和各种各样串行通信接口。但是,Arm 内核可以与第二个 32 位 RISC-V 内核共用总线(图 1)这个第二内核不是 MAX78000EXG+ 值得一看的唯一原因。该微控制器还带有一个 442 千字节 (Kb) 的加权卷积神经网络 (CNN) 加速器,用于人工智能 (AI) 模式匹配。RISC-V 内核在这里主要充当可编程智能直接存储器访问 (DMA) 器件,以在 CNN 和片载存储器之间进行数据移动。但是,RISC-V 内核也可以独立使用,从技术上来看,MAX78000EXG+ 就是一个双核处理器。

图 1:Maxim Integrated MAX78000EXG+ 微控制器带有一个具有 FPU 的 Arm Cortex-M4 内核以及一个 RISC-V 内核,同时提供各种各样的串行接口,以及用于 AI 处理的 CNN。(图片来源:Maxim Integrated)

图 1:Maxim Integrated MAX78000EXG+ 微控制器带有一个具有 FPU 的 Arm Cortex-M4 内核以及一个 RISC-V 内核,同时提供各种各样的串行接口,以及用于 AI 处理的 CNN。(图片来源:Maxim Integrated)

现在,我可以对 RISC-V 和 Arm 架构各种变型和生态系统做一个对比,但是,有一个事实真相是,即每当某个工程团队寻求其雇主没有使用过的新微控制器架构时,他们都要面临被踢出局的决定。例如,模块制造面临着其产品被集成商拒绝的风险,因为其产品中使用的主要内核不流行,或者用一个较模糊的词来说就是“行业不接受”。我在半导体公司时遇到过这种情况,当时访问的是一家数码相机模块制造商。

该公司做的数码相机模块很不错,但基于很利基的数字信号处理器 (DSP),我之所说是“利基”,是因为我估计这种处理器的市场占有率不到 DSP 市场的 10%。尽管这种数码相机模块有令人印象深刻的统计数据,而且我也有灵巧的 PPT 和高度发达的语言沟通技巧,但一开始我就是无法说服模块制造商使用我的 DSP。

正如预期那样,该模块制造商接触的数码相机集成商对其利基的 DSP 并没有什么热情。尽管该模块性能优势明显,但是就是没有相机集成商愿意与其合作和购买其模块。这个利基 DSP 内核参数规格高,便有太多未知因素,市场应用不足,大家都担心这个 DSP 会停产。经过快速调整,模块制造商回来找我,我们把他们的代码移植到我们的 DSP 上。

寻求使用新内核的另一个顾虑是,工程师对其架构没有足够的经验。在这种情形下,他们会低估新内核执行其应用的效率,或实际存储空间要求。与使用稳压器不同,在发现所选的内核性能不佳之前,可能要花上好几个月的开发时间,甚至会出现应用常见的特征蠕变。

很显然,通过推出 MAX78000EXG+,Maxim Integrated 已经解决了采用 RISC-V 内核的这种工程和商业风险。当不使用智能 DMA 时,RISC-V 内核可以在应用中用作第二内核。由于有 Cortex-M4 及其配套 PFU,因此任何对于性能的担心都可以放到一边。

结语

寻求使用像 RISC-V 这样的新内核,就应用性能而言,可能会带来不确定性。用途适合性和存储空间要求尚未确定,在其功能被完全理解和认可前,可能要花费数月时间写代码。不过,Maxim Integrated MAX78000EXG+ 使用了 Arm 内核,使得减少在新应用中采用 RISC-V 内核的技术和商业风险成为可能,但这是工程界的一大讽刺。

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum