制造商零件编号 LOFIVE-R1

SIFIVE FE310-G002 RISC-V DEV

GroupGets LLC

Developing a CPU design is a lengthy and costly process, and vendors like ARM charge royalties for the use of their designs to cover the development cost. Furthermore, details are sometimes kept secret, which makes it hard to understand the reason behind certain design choices. Additionally, this also makes it practically impossible to use such a proprietary design in an academic context. To solve those problems, the RISC-V project was started.

The concepts of modern Reduced Instruction Set Computers (RISC) date back to the 1980s. In short, the main idea is to make the hardware simpler by having a reduced number of simple instructions for loading, evaluating, and storing data. In contrast, the Complex Instruction Set Computer (CISC) architecture utilizes complex instructions that typically include the load and store steps. Both ideas aim to make CPUs faster -- RISC by reducing the cycles per instructions at the cost of the overall number of instructions per application, and CISC by minimizing the number of instructions per program at the cost of more complex hardware.

What differentiates RISC-V from other Instruction Set Architectures (ISA) is that the standard is open-source and free for personal, academic, and commercial use. Furthermore, it defines a base that handles the most important features in a CPU. It, alone, can implement a simplified general-purpose computer. This base can get extended by using extensions, which are specified to work with the base and with each other without conflict.

As an example, you can implement a CPU with a 64-bit Base Integer Instruction Set and include an extension to support Single-Precision Floating-Point instructions, and another one for Integer multiplication and division.

RISC-V has 32 registers (16 in the embedded variant). A floating-point extension implements 32 additional registers. All instructions address registers, except for memory access instructions, which makes RISC-V a load-store architecture. The first register always contains a value of zero. Some instructions also support immediate values.

Besides typical jumps and branches, RISC-V also contains support for subroutine calls. Furthermore, the standard supports computer systems that share memory between multiple CPUs and threads. For that purpose, it defines minimal support in the base instruction set. However, an atomic memory operation extension exists to allow for better support.

There are already a few manufacturers that implement the RISC-V ISA, and you can also choose from a wide variety of development boards that use such a CPU.

One of them is the LoFive R1, which is a gentle and affordable introduction to the RISC-V ecosystem. It comes with all the features you’d expect from a development board, like an Arduino, for a low price.

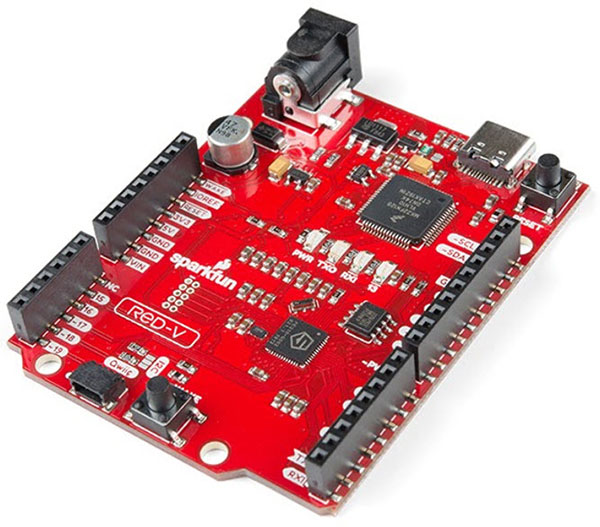

The SparkFun RED-V is another low-cost entry-level device that comes in the same form-factor as the well-established Arduino Uno R3, which makes this the optimal device for somebody looking to replace an Arduino in an existing design.

Image source: SparkFun

The Seeed Studio GAPUino is another development board that is fully pin-compatible with the popular Arduino Uno R3. However, it’s less affordable compared to the first two evaluation boards.

You can find detailed descriptions of these devices as well as many more RISC-V development boards in the DigiKey online catalog. The official RISC-V website also contains a list of boards and CPUs that implement the standard.

RISC-V is an open-source and royalty-free ISA standard that relies on the RISC architecture. This means that the hardware is less complicated, and the instruction set contains fewer instructions, compared to a CISC architecture. However, on average more instructions are needed per computer program. There are already a few manufacturers that implement the ISA in their CPUs, and you can already choose from a wide variety of affordable development boards that use such a processor.