如何选择用于逻辑电路或栅极设计的 MOSFET

MOS(金属氧化物半导体)系列的场效应晶体管也称为 MOSFET,是常见高压高电流电压驱动型开关应用的首选半导体。它们比其电流驱动型前身 BJT(双极结型晶体管)更受欢迎。在开关应用的另一端,逻辑电平 MOSFET 在处理器和其他小信号器件的构造中占主导地位,这主要是由于其具有更高的效率和高速开关能力。

就配置而言,MOSFET 的内部工作方式与 BJT 明显不同,但仍在发生导电性的地方使用带有增强型或耗尽型沟道的 N 和 P 结。有关 MOSFET 结构和操作的基本说明,请查看 Digi-Key Electronics 在 eewiki 上的文章。

许多微控制器试验板或 PCB 项目指定 TTL 逻辑使用 BJT 晶体管,例如常见的 2N3904 (NPN) 或 2N3906 (PNP)。它们确实在有或没有预偏置基极的情况下都性能良好,但效率较低,并且在某些情况下响应时间比同类 CMOS 产品慢。

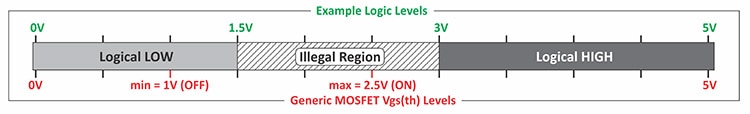

无论是使用 3.3 V 还是 5 V 逻辑,这些电压与接地之间都有阈值,这些阈值决定了逻辑上的高或低。此外,还需要高电平和低电平之间的一系列电压充当缓冲区,通常称为“非法”区域,以确保固态高电平和固态低电平之间的临界点不会太突然,否则可能会导致输出无法预测(图 1)。

选择逻辑电平 N 沟道 MOSFET 时要考虑的参数

栅极-源极阈值电压 - Vgs(th)(min) 和 Vgs(th)(max):等于或低于最小阈值的栅极电压会关闭 MOSFET。5 V 逻辑的常见最小栅极电压可能介于 0.5 V 至 1 V 之间。高于最大阈值的栅极电压会打开 MOSFET。介于最小值和最大值之间的栅极阈值电压可能会打开或关闭 MOSFET,因此必须加以避免。请注意,图 1 中最小值和最大值之间的区域如何与非法区域大致重合。

图 1

图 1

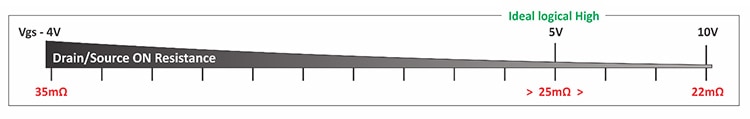

漏极-源极导通电阻 - Rds(on):导通时,漏极与源极之间会存在电阻,而且该电阻随栅源电压或 Vgs 的增加而减小。请选择一个 MOSFET,其最低 Rds(on) 值出现在或接近理想的逻辑高电压值,并且在较高的 Vgs 值下不会明显降低。请见图 2。

图 2

图 2

示例:根据规格书,Infineon 的 IRLZ44 MOSFET 在 5 V 时的漏源电阻为 25 mΩ,在 4 V 时为 35 mΩ,在 10 V 时为 22 mΩ。在 5 V 时,其 Rds(on) 值仅比 10 V 时的值高 3 mΩ,但比 4 V 时的 Rds(on) 值低 10 mΩ,因此就 Rds(on) 而言,它是一个不错的选择。

图 3

图 3

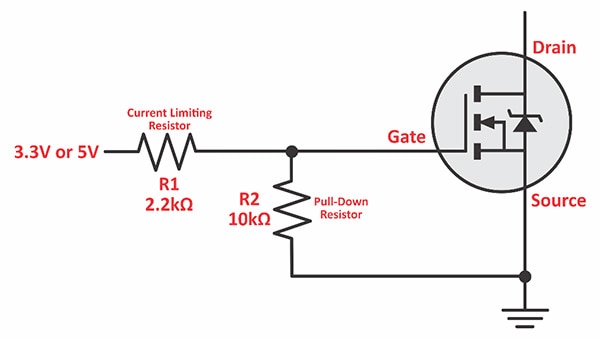

输入电容 - Ciss:MOSFET 的栅极、氧化层和主体连接的组合充当一个小型电容,当栅极上有电压时开始充电。充电需要时间,从而会导致导通状态延迟。因此,需选择输入电容尽可能最低的 MOSFET,以避免长时间延迟并尽量减小冲涌电流;该冲涌电流最初可能非常高,但会随着电容充电而减小。理想情况下,导通状态延迟极短,但可能会产生足够的浪涌,从而损坏电流输出容量有限的 I/O 引脚。

在引脚和栅极之间放置限流电阻,可防止 I/O 引脚消耗过多的电流。

若使用直接连接到微控制器输出引脚的 MOSFET,应根据需要使用外部电阻将 MOSFET 栅极上拉或下拉,以防 MCU 启动和复位期间 MOSFET 产生浮置栅极逻辑和不必要的输出。

在为逻辑电路或栅极设计选择 MOSFET 时,您可以从上述参数入手并进行微调,同时还要考虑散热和其他性能参数。请在下一个项目设计中大胆尝试 MOSFET 吧。

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum