高速DAC相位噪声大?很可能是时钟噪声惹的祸,本文教你消除它~

在所有器件特性中,噪声可能是一个特别具有挑战性、难以掌握的设计课题。本文主要介绍时钟噪声对于高速DAC相位噪声的影响。

DAC相位噪声来源

对于高速DAC来说,相位噪声主要来自以下几个方面:时钟噪声、电源噪声,以及内部噪声与接口噪声。

图1:DAC相位噪声来源 (图片来源:ADI)

图1:DAC相位噪声来源 (图片来源:ADI)

其中最重要的两个来源是时钟噪声与电源噪声。本文将主要介绍时钟噪声对于DAC相位噪声的影响。

→ 深入了解ADI的DAC芯片产品,点击这里>>

时钟相位噪声的产生

DAC时钟是DAC中产生相位噪声的首要原因。时钟决定何时发送下一样本,故相位(或时序)中的任何噪声都会直接影响输出的相位噪声。

图2:时钟与相位噪声的相关性(图片来源:ADI)

图2:时钟与相位噪声的相关性(图片来源:ADI)

如上图所示,时钟对相位噪声的影响,可以视作各相继离散值与一个矩形函数相乘,其时序由时钟定义。

图 3 相位噪声卷积(图片来源于ADI)

图 3 相位噪声卷积(图片来源于ADI)

如上图所示,在频域中,乘法转换为卷积运算。结果,期望的频谱被时钟相位噪声所破坏。

信号频率与相位噪声

信号频率与时钟频率之比,相对于载波的噪声放大或缩小,信号频率每降低一半,噪声改进6 dB。为了证明这一点,下图是不同频率(5GHz、1GHz、500MHz)下,混入一个带有轻度100kHz相位偏移的调制时钟信号(精密受控),来模拟相位噪声,来看看信号频率与相位噪声的关系。

图4:带100kHz相位调制的时钟输出相位噪声 (图片来源:ADI)

图4:带100kHz相位调制的时钟输出相位噪声 (图片来源:ADI)

我们可以看到,从5GHz时钟到500MHz DAC输出观测20dB降幅,从500MHz输出到1GHz输出观测到6dB增幅。

降低DAC相位噪声

选择一个性能良好的晶振,对于处理相位噪声可以达到事半功倍的效果。

在DigiKey中文技术论坛中,汇集了广大电子圈工程师日常所需的技术资源库,里面也有不少与晶振选型和降低DAC相位噪声相关的帖子,详情可以访问——电子元器件选型基础-晶振。

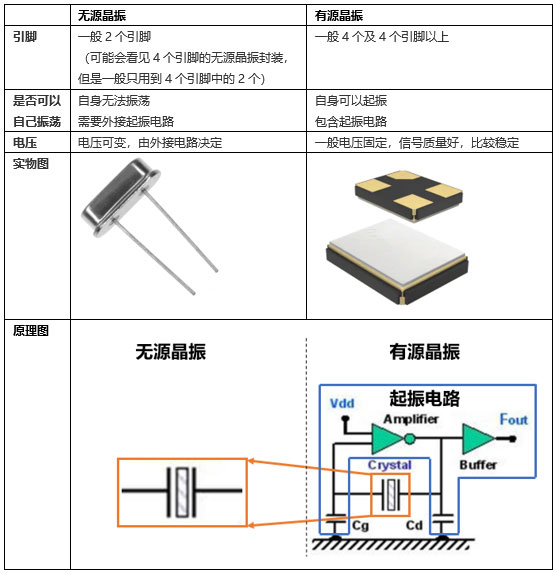

晶振可以分为有源晶振和无源晶振两种,下表对两种晶振进行了比较:

对于不同类型晶振特点和典型应用的比较,下表中做了详细地分析:

| 晶振类型 | 特点 | 应用 |

| 标准晶体振荡器(XO) | 最基本的一种是晶体振荡器 | 应用广泛 |

| 温度补偿振荡器(TCXO) | 进行温度补偿,使得输出频率更加稳定 | 适用于环境温度变化较大的场合,动态环境的应用。如蜂窝电话,智能手机等 |

| 压控振荡器(VCXO) | 输出频率由输入电压控制 | 常见于锁相环,混频器,讯号产生器等 |

| 恒温晶体振荡器(OCXO) | 使晶体振荡器的温度保持恒定,从而使得输出频率更加稳定 | 常见于对于频率稳定性要求比较高的场合 |

想了解如何通过DigiKey网站,快速进行低相位噪声晶振的选型,可以参考下面这篇文章——如何选择低相位噪声晶振?

本文小结

综上所述,了解噪声发生的原因,我们才能对症下药。时钟噪声对于DAC相位噪声的影响很大,因此选择一个高精度的晶振可能是最简单可行的方案。

最后,如果大家喜欢这篇文章吗,敬请快分享+点赞! ,也欢迎大家在文未留言讨论。

更多有关噪声技术的文章,请参阅以下文章:

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum