FPGA 基础知识 — 第 5 部分:Intel (Altera) 的 FPGA 使用入门

投稿人:DigiKey 北美编辑

2020-05-07

编者按:最佳处理解决方案常常是由 RISC、CISC、图形处理器与 FPGA 的组合提供,或由 FPGA 单独提供,或以硬处理器内核作为部分结构的 FPGA 提供。然而,许多设计人员不熟悉 FPGA 的功能、其发展脉络以及如何使用 FPGA。本系列文章由多个部分组成。第 1 部分详细介绍了 FPGA;第 2 部分聚焦于来自 Lattice Semiconductor 的 FPGA 产品;第 3 部分着重介绍了 Microchip Technology(来自子公司 Microsemi Corporation)的 FPGA 器件系列和设计工具。第 4 部分深入讨论 Xilinx 的元器件和工具。本文为第 5 部分,其中将介绍 Altera 的产品,Altera 被 Intel 收购,如今是 Intel 的可编程解决方案事业部(后文将使用 Intel 指代)。

如第 1 部分所述,现场可编程门阵列 (FPGA) 具有诸多特性,无论是单独使用,抑或采用多样化架构,皆可作为宝贵的计算资产;但是许多设计人员并不熟悉 FPGA,亦不清楚如何将这类器件整合到设计中。解决办法之一是深入研究主要供应商提供的 FPGA 架构及相关工具。

FPGA 选件高级概述

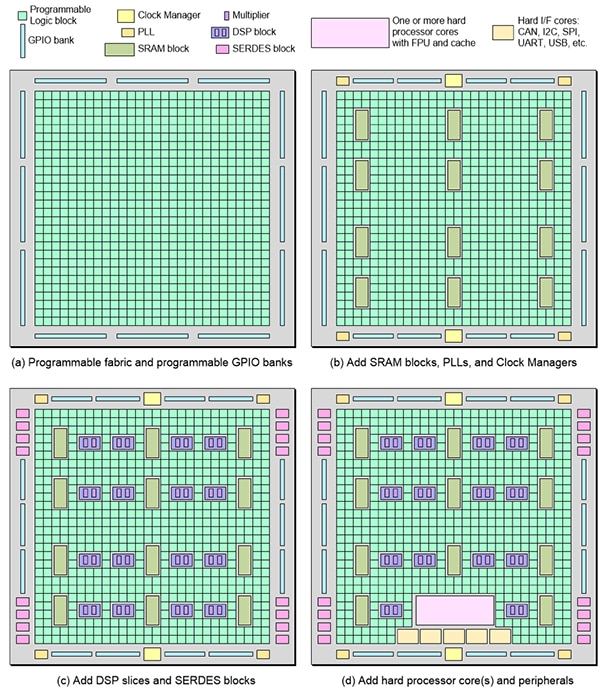

市场上有许多不同类型的 FPGA,每种类型都有不同的功能和特性组合。可编程结构是任何 FPGA 的核心,它以可编程逻辑块阵列的形式呈现,也称为逻辑元件 (LE)(图 1(a))。FPGA 结构可进一步扩展,以包括 SRAM 块(称为块 RAM (BRAM))、锁相环 (PLL) 和时钟管理器之类的东西(图 1(b))。此外,还可以添加数字信号处理 (DSP) 块(称为 DSP 切片)和高速串行器/解串器 (SERDES)(图 1(c))。

图 1:最简单的 FPGA 仅包含可编程结构和可配置通用 IO (GPIO) (a);不同架构是在此基本结构上增加其他元件而形成:SRAM 块、PLL 和时钟管理器 (b);DSP 块和 SERDES 接口 (c);以及硬处理器内核和外设 (d)。(图片来源:Max Maxfield)

图 1:最简单的 FPGA 仅包含可编程结构和可配置通用 IO (GPIO) (a);不同架构是在此基本结构上增加其他元件而形成:SRAM 块、PLL 和时钟管理器 (b);DSP 块和 SERDES 接口 (c);以及硬处理器内核和外设 (d)。(图片来源:Max Maxfield)

外设接口功能(如 CAN、I2C、SPI、UART 和 USB)可以实现为可编程结构中的软内核,但许多 FPGA 将其作为硬内核在硅片中实现。同样,微处理器也可以实现为可编程结构中的软内核,或作为硬内核在硅片中实现(图 1(d))。具有硬处理器内核的 FPGA 称为片上系统 (SoC) FPGA。不同 FPGA 针对不同的市场和应用提供不同的功能、特性和容量集合。

FPGA 供应商有很多,包括 Intel(收购了 Altera)、Efinix、Lattice Semiconductor、Microchip Technology(收购了 Atmel 和 Microsemi),以及 Xilinx。

所有这些供应商都提供多个 FPGA 系列:有的提供 SoC FPGA,有的提供面向人工智能 (AI) 和机器学习 (ML) 应用的器件,有的则提供适用于航天应用的耐辐射器件。由于产品系列众多,每个系列提供不同的资源,因此为眼前的任务选择最佳器件可能很棘手。

Intel FPGA 和 SoC FPGA 介绍

Intel 提供各种各样的可编程器件产品,性能和功能从中等到极高都有,并涵盖传统 FPGA 到 SoC FPGA(即,将 FPGA 可编程结构和一种或多种强化处理器内核结合在一起的器件)。

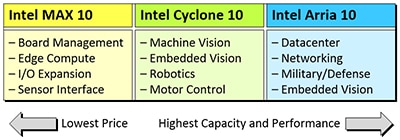

Intel 的产品系列当前有五个主动 FPGA 系列,包括 Max 10、Cyclone 10,和 Arria 10(图 2)。Intel 还提供极高端的 Stratix 10 及其更新的最先进 Agilex 器件。

图 2:在 Intel 的五个 FPGA 系列中,其中三个(从成本最低 (Max 10) 到最高容量及性能 (Arria 10))的目标应用和市场覆盖从板卡管理和 I/O 扩展,一直到嵌入式视觉和军事/国防。Stratix 10 和更新的 Agilex 器件进一步提升了性能。(图片来源:Max Maxfield)

图 2:在 Intel 的五个 FPGA 系列中,其中三个(从成本最低 (Max 10) 到最高容量及性能 (Arria 10))的目标应用和市场覆盖从板卡管理和 I/O 扩展,一直到嵌入式视觉和军事/国防。Stratix 10 和更新的 Agilex 器件进一步提升了性能。(图片来源:Max Maxfield)

Intel 的 Max 10 FPGA 集成片载 NOR 闪存,以提供 FPGA 配置。其他产品系列有基于 SRAM 的配置单元,并且会在上电时从板载外部存储器件或系统的其他位置(如在外部处理器的控制之下)加载配置。除 MAX 10 系列以外,所有其他 Intel FPGA 系列都可作为 FPGA 或 SoC FPGA 的形式提供,并与强化微处理器系统集成。

MAX 10 FPGA 的集成功能包括模数转换器 (ADC) 和双通道配置闪存,后者可提供在单个芯片上存储与动态切换两张图像的功能。MAX 10 FPGA 还具有 Nios II 软核心处理器支持、DSP 块和软双倍数据速率 3 (DDR3) 存储控制器。

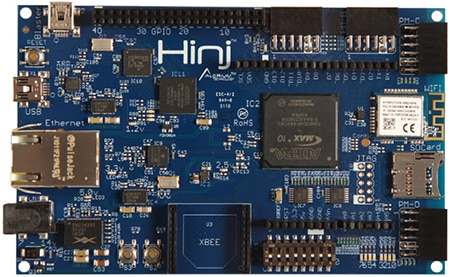

MAX 10 产品组合中的代表性器件是 10M16SCU169I7P。该产品具有 16,000 个逻辑单元和 130 个输入/输出 (I/O),而且总 RAM 位数为 562,176。Intel 的 EK-10M08E144 是适用于 MAX 10 的评估板,另一个是 HINJKIT,这是 Alorium Technology, LLC 的 FPGA 物联网传感器集线器开发套件(图 3)。尤其值得关注的是,HINJKIT 的 MAX 10 FPGA 包括 Alorium Technology 的 AVR 兼容 8 位微控制器,使 HINJKIT 能与 Arduino IDE 配合使用。该板还可为第三方物联网载板、模块和配件提供高度的接口灵活性。

图 3:HINJKIT 是 Alorium 的 MAX 10 FPGA 开发平台,可为第三方物联网载板、模块和配件提供高度的接口灵活性。(图片来源:Alorium Technology)

图 3:HINJKIT 是 Alorium 的 MAX 10 FPGA 开发平台,可为第三方物联网载板、模块和配件提供高度的接口灵活性。(图片来源:Alorium Technology)

Intel 的 Cyclone 10 GX FPGA 提供 12.5 GB 基于收发器的功能、1.4 Gbit/s 低压差分信号 (LVDS),以及适用于最高 1,866 Mbits/s 数据速率的高达 72 位宽 DDR3 SDRAM 接口。Cyclone 10 GX FPGA 针对机器视觉、视频连接和智能视觉相机等高带宽性能应用进行了优化。

与之相比,Cyclone 10 LP FPGA 则针对低静态功耗、低成本应用进行了优化,例如 I/O 扩展、传感器融合、电机/运动控制、芯片到芯片桥接以及控制应用。GX 和 LP 器件系列都支持垂直迁移,使设计人员从一个器件开始着手设计,然后在未来迁移到相邻密度。

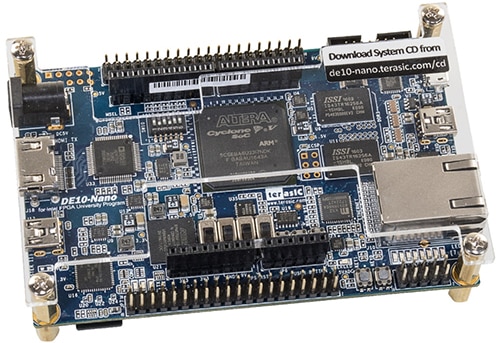

Cyclone 10 产品组合中的代表性器件是 10CL006YU256A7G。该产品具有 6,272 个逻辑单元和 176 个 I/O,而且总 RAM 位数为 276,480。相关的开发和评估板及模块还有很多,包括 P0496 DE10-NANO Cyclone V SE SoC 套件(图 4)、P0553 TSoM Cyclone V SE 评估板(也基于 Cyclone V SoC FPGA)和 P0581 TSoM Cyclone V SE FPGA 评估板,它们都是 Terasic Inc 的产品。(注意,这些板上的 Cyclone V FPGA 是 Cyclone 10 系列的较早期产品。)

图 4:低成本 P0496 DE10-NANO 开发套件拥有强大的硬件设计平台,让用户可以试验与评估 Cyclone FPGA。(图片来源:Terasic Inc.)

图 4:低成本 P0496 DE10-NANO 开发套件拥有强大的硬件设计平台,让用户可以试验与评估 Cyclone FPGA。(图片来源:Terasic Inc.)

Arria 10 器件基于 TSMC 的 20 纳米 (nm) 工艺技术,将双核 Arm Cortex-A9 MPCore 硬处理器系统 (HPS) 与可编程结构组合在一起,该结构还包括强化浮点 DSP 块。Arria 10 还装载了嵌入式高速收发器、硬存储控制器,以及协议知识产权 (IP) 控制器,全都包含在单个高度集成的封装中。

Arria 10 产品组合中的代表性器件是 10AX022C4U19E3SG。该产品具有 220,000 个逻辑单元和 240 个 I/O,而且总 RAM 位数为 13,752,320。Intel 的 DK-DEV-10AX115S-A Arria 10 GX FPGA 评估板(图 5)是开发此 FPGA 的合适平台。该板让设计人员能够开发与测试基于 Arria 10 的 PCI Express (PCIe) 3.0 设计;开发与测试由 DDR4、DDR3、QDR IV 和 RLDRAM III 存储器组成的存储器子系统;并且通过使用 FPGA 夹层卡 (FMC) 连接器连接到由 Intel 合作伙伴提供的 FMC 夹层卡,来开发模块化的可扩展设计。

图 5:DK-DEV-10AX115S-A Arria 10 GX FPGA 开发套件提供一个完整的设计环境,包括开发与测试基于 PCIe 的设计、存储器子系统和基于 FMC 卡的系统所需的全部硬件和软件。(图片来源:Intel)

图 5:DK-DEV-10AX115S-A Arria 10 GX FPGA 开发套件提供一个完整的设计环境,包括开发与测试基于 PCIe 的设计、存储器子系统和基于 FMC 卡的系统所需的全部硬件和软件。(图片来源:Intel)

Intel 的 Stratix 10 FPGA 和 SoC FPGA 采用 Intel Hyperflex FPGA 架构。此器件产品线中的 FPGA 可应对高吞吐量系统的需求,其具有最高 10 TFLOPS 的浮点性能,并支持从 28.3 Gbits/s (GX) 到 57.8 Gbits/s 收发器,后者在最多 144 个收发器通道中,能够满足 5G 通信、云计算、网络虚拟化和光纤传输网络的带宽要求。产品变体包括 PCIe Gen4 接口,最高能以每秒传输 16 GB 的速度 (GT/s) 提供 x16 配置,以及一种可支持特定 Intel Optane DC 永久性存储器的全新存储控制器。

Intel 的 DK-DEV-1SGX-L-A Stratix 10 GX FPGA 评估板(图 6)支持利用 Stratix 10 产品线进行开发。该板让设计人员能够开发与测试基于 Stratix 10 的 PCI Express (PCIe) 3.0 设计;开发与测试由 DDR4、DDR3、QDR IV 和 RLDRAM III 存储器组成的存储器子系统;并且通过使用 FPGA 夹层卡 (FMC) 连接器连接到同样由 Intel 合作伙伴提供的 FMC 夹层卡,开发模块化的可扩展设计。

图 6:DK-DEV-1SGX-L-A Stratix 10 GX FPGA 评估板提供一个完整的设计环境,包括开发与测试基于 PCIe 的设计、存储器子系统和基于 FMC 卡的系统所需的全部硬件和软件。(图片来源:Intel)

图 6:DK-DEV-1SGX-L-A Stratix 10 GX FPGA 评估板提供一个完整的设计环境,包括开发与测试基于 PCIe 的设计、存储器子系统和基于 FMC 卡的系统所需的全部硬件和软件。(图片来源:Intel)

使用 Intel 的 FPGA 和 SoCs FPGA 进行设计和开发

在本 FPGA 系列文章的第 1 部分中,我们指出这些器件的传统设计方法是让工程师使用 Verilog 或 VHDL 等硬件描述语言 (HDL),在抽象级别(即寄存器传送级 [RTL])上捕获设计意图。首先可以对这些 RTL 描述进行仿真,以验证其是否符合要求,然后将其传送给综合工具,生成用于对 FPGA 进行配置(编程)的配置文件。

抽象的下一步是捕获设计意图,主要是使用 C/C++ 之类的编程语言或 SystemC 这样的特殊实现工具;后者是一组 C++ 类和宏,可提供事件驱动的仿真接口。这些方法有助于并发进程的仿真,每个进程都使用简单的 C++ 语法进行描述。对于此类描述,可以通过像常规程序一样运行来进行分析和配置,然后传递给高级综合 (HLS) 引擎,由该引擎输出 RTL,而 RTL 会传输至常规综合引擎。

Open CL(开放运算语言)在概念上更加抽象,该框架适用于编写可跨异构平台执行的程序。除了 FPGA,这些平台还包括中央处理单元 (CPU)、图形处理单元 (GPU)、数字信号处理器 (DSP),以及其他处理器或硬件加速器。OpenCL 指定用于为这些器件进行编程的编程语言(基于 C99 和 C++11),并且指定应用程序编程接口 (API),以对平台进行控制并在运算设备上执行程序。

对于 Intel FPGA 和 SoC FPGA,用户使用 Intel 的 Quartus Prime 设计软件为所有产品系列开发设计。该软件分为三个版本:Quartus Prime Pro Edition、Quartus Prime Standard Edition 和 Quartus Prime Lite Edition。Pro 和 Standard Edition 需要付费许可证,而 Lite Edition 可供免费下载。

Pro Edition 经过优化,可借助 Agilex、Stratix 10、Arria 10 和 Cyclone 10 GX 器件系列支持下一代 FPGA 和 SoC FPGA 中的高级功能;Standard Edition 广泛支持 Cyclone 10 LP 器件系列及其他更早期的器件系列;而 Lite Edition 可免费下载而无需许可证文件,为大容量器件系列提供理想的切入点。

Intel 提供各式各样的其他设计工具和资源,包括 Intel DSP Builder、Intel 高级综合 (HLS) 编译器,以及 Intel FPGA SDK for OpenCL。

Intel Distribution of the OpenVINO Toolkit 也非常实用,可帮助开发人员构建人工智能 (AI)、计算机视觉、音频、语音和语言应用程序,实现从边缘至云的深度学习推理。除了 FPGA,该工具套件还支持使用常见的 API,跨 Intel 架构和 AI 加速器(CPU、iGPU、Intel 的 Movidius 视觉处理单元 (VPU) 和 Intel 的 Gaussian & Neural Accelerator (GNA))异构执行。该工具套件由基于 Cyclone V GT FPGA 的 OpenVINO 入门套件提供支持。

总结

最佳处理设计解决方案常常是由处理器与 FPGA 的组合提供,或由 FPGA 单独提供,或以硬处理器内核作为部分结构的 FPGA 提供。作为一项技术,FPGA 多年来发展迅速,能够满足灵活性、处理速度、功耗等多方面的设计需求,非常适合智能接口、机器视觉和人工智能等众多应用。

Intel 提供从低到极高范围、从传统 FPGA 到 SoC FPGA 的可编程器件产品。如上所述,要使用此类器件进行设计,Intel 和其他第三方都提供强大的开发套件和工具,以满足硬件开发人员、软件开发人员以及人工智能和计算机视觉系统构建者的需求。

拓展阅读

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。