FPGA 基础知识 – 第 4 部分:Xilinx 的 FPGA 入门

投稿人:DigiKey 北美编辑

2020-04-01

编者按:最佳处理解决方案常常是由 RISC、CISC、图形处理器与 FPGA 的组合提供,或由 FPGA 单独提供,或以硬处理器内核作为部分结构的 FPGA 提供。然而,许多设计人员不熟悉 FPGA 的功能、其发展脉络以及如何使用 FPGA。 本系列文章由多个部分组成,第 1 部分详细介绍了 FPGA;第 2 部分聚焦于来自 Lattice Semiconductor 的 FPGA 产品;第 3 部分着重介绍了 Microchip Technology(来自子公司 Microsemi Corporation)的 FPGA 器件系列和设计工具。本文是第 4 部分,讨论了来自 Xilinx 的元器件和工具。第 5 部分将关注来自 Altera 的产品。

如第 1 部分所述,现场可编程门阵列 (FPGA) 具有诸多特性,无论是单独使用,抑或采用多样化架构,皆可作为宝贵的计算资产;但是许多设计人员并不熟悉 FPGA,亦不清楚如何将这类器件整合到设计中。

解决办法之一是深入研究主要供应商提供的 FPGA 架构及相关工具;本文则从 Xilinx 产品系列开始着手。

FPGA 选件高级概述

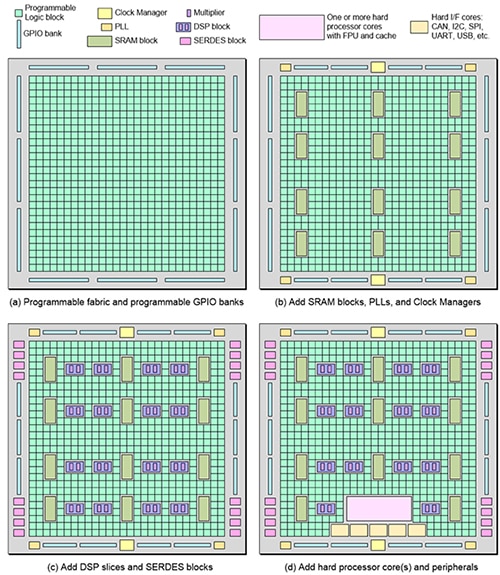

市场上有许多不同类型的 FPGA,每种类型都有不同的功能和特性组合。可编程结构是任何 FPGA 的核心,它以可编程逻辑块阵列的形式呈现,也称为逻辑元件 (LE)(图 1a)。FPGA 结构进一步扩展可包括 SRAM 块(称为块 RAM (BRAM))、锁相环 (PLL) 和时钟管理器之类的东西(图 1b)。此外,还可以添加数字信号处理 (DSP) 块(称为 DSP 切片)和高速串行器/解串器 (SERDES)(图 1c)。

图 1:最简单的 FPGA 仅包含可编程结构和可配置通用 IO (GPIO) (a);不同架构是在此基本结构上增加其他元件而形成:SRAM 块、PLL 和时钟管理器 (b);DSP 块和 SERDES 接口 (c);以及硬处理器内核和外设 (d)。(图片来源:Max Maxfield)

图 1:最简单的 FPGA 仅包含可编程结构和可配置通用 IO (GPIO) (a);不同架构是在此基本结构上增加其他元件而形成:SRAM 块、PLL 和时钟管理器 (b);DSP 块和 SERDES 接口 (c);以及硬处理器内核和外设 (d)。(图片来源:Max Maxfield)

外设接口功能(如 CAN、I2C、SPI、UART 和 USB)可以实现为可编程结构中的软内核,但许多 FPGA 将其作为硬内核在硅片中实现。同样,微处理器也可以实现为可编程结构中的软内核,或作为硬内核在硅片中实现(图 1d)。具有硬处理器内核的 FPGA 称为片上系统 (SoC) FPGA。不同 FPGA 针对不同的市场和应用提供不同的功能、特性和容量集合。

FPGA 供应商有很多,包括 Altera(被 Intel 收购)、Atmel(被 Microchip Technology 收购)、Efinix、Lattice Semiconductor、Microsemi(也被 Microchip Technology 收购)和 Xilinx。

所有这些供应商都提供多个 FPGA 系列;有的提供 SoC FPGA,有的提供面向人工智能 (AI) 和机器学习 (ML) 应用的器件,有的则针对航天等高辐射环境提供耐辐射器件。由于产品系列众多,每个系列提供不同的资源,因此为眼前的任务选择最佳器件可能很棘手。

Xilinx 的 FPGA、SoC、MPSoC、RFSoC 和 ACAP 产品介绍

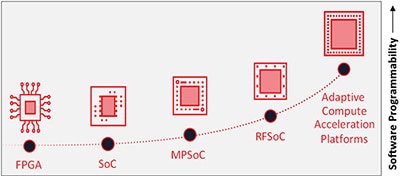

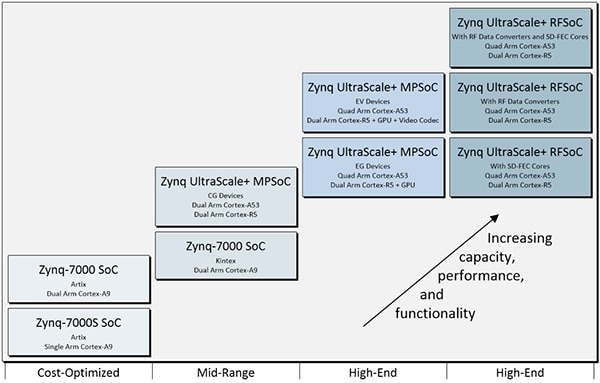

Xilinx 提供各种各样的可编程器件产品,性能和功能从中等到极高都有。范围从传统的 FPGA 到 SoC(具有单个硬核心处理器的 FPGA 可编程结构)、MPSoC(具有多个硬核心处理器的 FPGA 可编程结构)、RFSoC(具有 RF 功能的 MPSoC)和 ACAP(自适应计算加速平台)(图 2)。

图 2:随着时间的推移,Xilinx 架构产品组合已经从仅包含可编程结构的简单 FPGA,一直演变到可编程结构使用硬核心处理器增强的 SoC 器件、具有多个处理器的 MPSoC、具有 RF 功能的 RFSoC,再到针对 AI 等应用的最新一代 ACAP。(图片来源:Max Maxfield)

图 2:随着时间的推移,Xilinx 架构产品组合已经从仅包含可编程结构的简单 FPGA,一直演变到可编程结构使用硬核心处理器增强的 SoC 器件、具有多个处理器的 MPSoC、具有 RF 功能的 RFSoC,再到针对 AI 等应用的最新一代 ACAP。(图片来源:Max Maxfield)

Xilinx 拥有非常广泛的产品组合,涉及非常多的细分市场,并提供了各种各样的部署方法,因此对于刚接触 FPGA 的新手来说,可能很难了解“全局”。

Xilinx 所耕耘的市场包括但不限于数据中心(计算、网络、存储);通信(有线、无线);航空航天与国防;工业、科学和医学 (ISM);测试、测量和仿真 (TME);以及汽车、广播和消费品。

对于部署方法,这些包括 Xilinx 自称的硬件自适应设备,其中包括芯片、评估板和开发套件;可部署的终端系统,包括系统级模块 (SoM) 和 PCIe 加速卡;以及 FPGA 即服务 (FAAS),包括通过领先的云提供商(包括 Amazon Web Services [AWS]、Alibaba.com 和 Nimbix.net)评估和利用 Xilinx 技术。

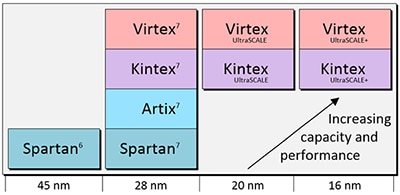

对于 Xilinx 的 FPGA 产品,一种分类方法是通过工艺技术节点(图 3)。

图 3:Xilinx 的 FPGA 产品提供了全面的多节点产品组合,可满足各种应用的需求。(图片来源:Max Maxfield)

图 3:Xilinx 的 FPGA 产品提供了全面的多节点产品组合,可满足各种应用的需求。(图片来源:Max Maxfield)

根据目标应用,设计人员可以选择基于较早的技术节点来实现低成本、小基底面的 FPGA,或者对于最新的网络应用等,选择基于最新技术节点来实现高容量、高带宽、高性能器件。

对于需要一个或多个硬处理器内核(以及 GPU、编解码器和软判决前向纠错 [SD-FEC] 内核等其他强化功能)的设计,Xilinx 提供了一个以 Zynq 命名的器件产品组合。Zynq 的 SoC、MPSoC 和 RFSoC 产品的摘要如图 4 所示。这套解决方案为设计人员提供了广泛的功能,能协助优化功耗、性能、成本和上市时间。

图 4:Xilinx 的 SoC、MPSoC 和 RFSoC 产品将处理器的软件可编程性与 FPGA 的硬件可编程性集成在一起,为设计人员提供了系统性能、灵活性和可扩展性。(图片来源:Max Maxfield)

图 4:Xilinx 的 SoC、MPSoC 和 RFSoC 产品将处理器的软件可编程性与 FPGA 的硬件可编程性集成在一起,为设计人员提供了系统性能、灵活性和可扩展性。(图片来源:Max Maxfield)

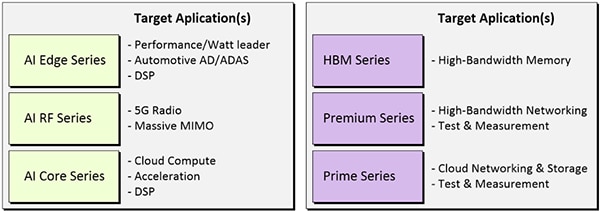

Xilinx 的最新产品是 Versal 自适应计算加速平台 (ACAP) 器件,所有这些器件均基于 7 纳米 (nm) 工艺技术节点来实现。ACAP 是高度集成的多核心计算平台,可以适应不断演进的各种算法。它们可以在硬件和软件级别进行动态定制,以适合各种应用和工作负载。ACAP 是围绕可编程片上网络 (NoC) 进行构建,硬件设计人员和软件开发人员都可以轻松对其进行编程。

Versal 器件的新功能包括智能引擎,即用于 ML 和 DSP 工作负载的大规模矢量处理器阵列;可移动 TB 级数据的高带宽、低延迟和低功耗可编程 NoC;以及一个集成的 Shell,可通过预先构建的核心基础结构和系统连接性来提高性能、利用率和生产率。

图 5 显示了 Versal ACAP 产品组合的概述。

图 5:Xilinx 的 Versal ACAP 是高度集成的多核心计算平台,可以适应不断演进的各种算法。ACAP 可以在硬件和软件级别进行动态定制,以适合各种应用和工作负载。(图片来源:Max Maxfield)

图 5:Xilinx 的 Versal ACAP 是高度集成的多核心计算平台,可以适应不断演进的各种算法。ACAP 可以在硬件和软件级别进行动态定制,以适合各种应用和工作负载。(图片来源:Max Maxfield)

正如将在设计工具部分中的讨论,有关 Versal 器件的一个关键区别是新的软件堆栈。该堆栈主要面向数据科学家和软件工程师,以及传统硬件设计工程师。

市场上有各种各样的 Xilinx 器件可供选择。一些代表性的产品是 Artix-7 FPGA、Kintex UltraScale FPGA、Kintex UltraScale+ FPGA、来自 Trenz Electronic GmbH 的 Zynq-7000 SoC 模块,以及 Zynq UltraScale+ MPSoC。

同样,也有各种各样的评估板和开发板可供选择。一些代表性的产品包括来自 Digilent 的 Artix-7 FPGA 评估板、来自 Analog Devices 的 Kintex UltraScale FPGA 评估板、来自 Xilinx 的 Kintex UltraScale+ FPGA 评估板、来自 Digilent 的 Zynq-7000 SoC FPGA 评估板,以及来自 Xilinx 的 Zynq UltraScale+ MPSoC FPGA 评估板。

使用 Xilinx 的 FPGA、SoC 和 ACAP 进行设计和开发

Xilinx 真正区别于竞争对手的一个因素是:设计工具和流程的广度和深度。

在本 FPGA 系列文章的第 1 部分中,我们指出这些器件的传统设计方法是让工程师使用 Verilog 或 VHDL 等硬件描述语言 (HDL),在抽象级别(即寄存器传送级 [RTL])上捕获设计意图。首先可以对这些 RTL 描述进行仿真,以验证其是否符合要求,然后将其传送给综合工具,生成用于对 FPGA 进行编程的配置文件。

抽象的下一步是捕获设计意图,主要是使用 C/C++ 之类的编程语言或 SystemC 这样的特殊实现工具;后者是一组 C++ 类和宏,可提供事件驱动的仿真接口。这些方法有助于并发进程的仿真,每个进程都使用简单的 C++ 语法进行描述。对于此类描述,可以通过像常规程序一样运行来进行分析和配置,然后传递给高级综合 (HLS) 引擎,由该引擎输出 RTL,而 RTL 会传输至常规综合引擎。

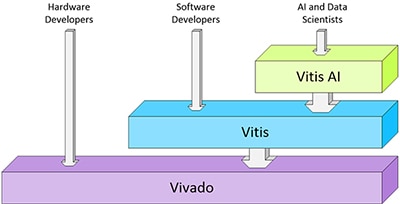

所有这些功能都包含在 Vivado 设计套件 HLx 版中,其输出是配置比特流,随后会加载到目标 FPGA、SoC、MPSoC、RFSoC 或 ACAP 器件中。除了允许硬件开发人员利用基于 C 语言的设计和经优化的设计复用,Vivado 还提供 IP 子系统复用、集成自动化和加速的设计收敛功能(图 6)。

图 6:Xilinx 的 Vivado 和 Vitis 设计工具堆栈的高级视图反映了用户如何能以最合适的抽象级别使用这些工具。硬件设计人员使用 Vivado,软件开发人员使用 Vitis,而 AI 和数据科学家使用 Vitis AI。(图片来源:Max Maxfield)

图 6:Xilinx 的 Vivado 和 Vitis 设计工具堆栈的高级视图反映了用户如何能以最合适的抽象级别使用这些工具。硬件设计人员使用 Vivado,软件开发人员使用 Vitis,而 AI 和数据科学家使用 Vitis AI。(图片来源:Max Maxfield)

下一个抽象级别由 Vitis 统一软件平台支持,该平台使软件开发人员能够无缝构建加速型应用。从概念上讲,Vitis 的上面是 Vitis AI,它让 AI 和数据科学家可以在 TensorFlow 抽象级别工作。Vitis AI 是在 Xilinx 硬件平台上进行 AI 推理的开发平台,同时包括边缘设备和 Alveo PCIe 卡。该平台由优化的 IP、工具、库、模型和示例设计组成,旨在充分利用 Xilinx 的 FPGA 和 ACAP 器件上的 AI 加速潜力。

Vitis AI 馈送至 Vitis,而 Vitis 自身馈送至 Vivado。图 6 中的关键点在于,用户仅“看到”他们需要“看到”的内容。也就是说,硬件开发人员将仅“看到”Vivado,软件开发人员将仅“看到”Vitis,而 AI 和数据科学家将仅“看到”Vitis AI。这样,用户就可以在最合适的抽象级别使用这些工具。

若为软件开发人员提供 Vitis 之类的工具套件,将他们与底层硬件隔离开来,便可使 FPGA 面向更多的开发人员开放。同样,若为 AI 和数据科学家提供 Vitis AI 之类的工具套件,使他们能够专注于自己的抽象级别并将其与底层软件隔离开来,则又会使 FPGA 面向新的开发人员群体开放。

在提供这些功能方面,Xilinx 走在了全行业的前沿,致力于将 FPGA 工具提升到更高的设计抽象级别,这将使开发人员能够更轻松地利用这些器件的功能,并将其集成到接下来的设计中。

总结

最佳处理设计解决方案常常是由处理器与 FPGA 的组合提供,或由 FPGA 单独提供,或以硬处理器内核作为部分结构的 FPGA 提供。作为一项技术,FPGA 多年来发展迅速,能够满足灵活性、处理速度、功耗等多方面的设计需求,非常适合智能接口、机器视觉和人工智能等众多应用。

如上所述,Xilinx 提供许多可编程器件产品,性能和功能从中等到极高都有。这些产品范围从传统的 FPGA 到 SoC(具有单个硬核心处理器的 FPGA 可编程结构)、MPSoC(具有多个硬核心处理器的 FPGA 可编程结构)、RFSoC(具有 RF 功能的 MPSoC)和 ACAP(自适应计算加速平台)。

为了帮助设计人员使用这些器件来构建设计,Xilinx 提供了一套工具来满足硬件开发人员 (Vivado)、软件开发人员 (Vitis) 以及 AI 和数据科学家 (Vitis AI) 的需求。

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。