FPGA 基础知识 – 第 3 部分:Microchip Technology 的 FPGA 使用入门

投稿人:DigiKey 北美编辑

2020-01-30

编者按:最佳处理解决方案常常是由 RISC、CISC、图形处理器与 FPGA 的组合提供,或由 FPGA 单独提供,或以硬处理器内核作为部分结构的 FPGA 提供。然而,许多设计人员不熟悉 FPGA 的功能、其发展脉络以及如何使用 FPGA。本系列文章由多个部分组成,第 1 部分详细介绍了 FPGA 的基本概念。第 2 部分重点介绍了 Lattice Semiconductor 的 FPGA 产品。本文是第 3 部分,聚焦于 Microchip Technology(通过子公司 Microsemi Corporation)提供的 FPGA 器件系列和设计工具。第 4 部分和第 5 部分将分别介绍 Altera 和 Xilinx 的 FPGA 及工具。

如第 1 部分所述,现场可编程门阵列 (FPGA) 具有诸多特性,无论是单独使用,抑或采用多样化架构,皆可作为宝贵的计算资产;但是许多设计人员并不熟悉 FPGA,亦不清楚如何将这类器件整合到设计中。

解决办法之一是深入研究主要供应商提供的 FPGA 架构及相关工具。本文将介绍 Microchip Technology 的产品系列。

高级 FPGA 选件概览

市场上有许多不同类型的 FPGA,每种类型都有不同的功能和特性组合。可编程结构是所有 FPGA 的核心,它以可编程逻辑块阵列的形式呈现,也称为逻辑元件 (LE)(图 1a)。FPGA 结构可进一步扩展,以包括 SRAM 块(称为块 RAM (BRAM))、锁相环 (PLL) 和时钟管理器之类的东西(图 1b)。此外,还可以添加数字信号处理 (DSP) 块(称为 DSP 切片)和高速串行器/解串器 (SERDES)(图 1c)。

图 1:最简单的 FPGA 仅包含可编程结构和可配置通用 IO (GPIO) (a);不同架构是在此基本结构上增加其他元件而形成:SRAM 块、PLL 和时钟管理器 (b);DSP 块和 SERDES 接口 (c);以及硬处理器内核和外设 (d)。(图片来源:Max Maxfield)

图 1:最简单的 FPGA 仅包含可编程结构和可配置通用 IO (GPIO) (a);不同架构是在此基本结构上增加其他元件而形成:SRAM 块、PLL 和时钟管理器 (b);DSP 块和 SERDES 接口 (c);以及硬处理器内核和外设 (d)。(图片来源:Max Maxfield)

外设接口功能(如 CAN、I2C、SPI、UART 和 USB)可以作为可编程结构中的软内核来实现,但许多 FPGA 将其作为硬内核在硅片中实现。同样,微处理器也可以实现为可编程结构中的软内核,或作为硬内核在硅片中实现(图 1d)。具有硬处理器内核的 FPGA 称为片上系统 (SoC) FPGA。不同 FPGA 针对不同的市场和应用提供不同的功能、特性和容量集合。

FPGA 供应商有很多,包括 Altera(被 Intel 收购)、Atmel(被 Microchip Technology 收购)、Lattice Semiconductor、Microsemi(也被 Microchip Technology 收购)和 Xilinx。

所有这些供应商都提供多个 FPGA 系列;有的提供 SoC FPGA,有的则针对航天等高辐射环境提供耐辐射器件。由于产品系列众多,每个系列提供不同的资源,因此为眼前的任务选择最佳器件可能很棘手。

Microchip Technology 的 FPGA 介绍

Microchip Technology 的 FPGA 产品范围覆盖中低端,以具有优异可靠性的低功耗、高安全性器件为主。Microchip 的 FPGA 广泛部署于有线和无线通信、国防和航空、工业嵌入式应用,拥有强大的 DSP 和存储器资源,并在硬件加速、人工智能、图像处理、边缘计算等应用中展示出了一定价值。

Microchip 推出了三个主要 FPGA 系列:

- IGLOO®2 FPGA:具有大量资源的低密度器件

- SmartFusion®2 SoC FPGA:具有大量资源和 32 位硬处理器内核的低密度器件

- PolarFire™ FPGA 和 SoC FPGA:成本经过优化的高性能器件,并采用 28 纳米 (nm) 工艺技术实现

所有 FPGA 都有配置单元,它们决定了每个可编程逻辑块的功能,以及逻辑块彼此之间和逻辑块与外部的连接方式。这些单元还可用于配置 GPIO 的接口标准、输入阻抗、输出压摆率等。

有些 FPGA 使用基于 SRAM 的配置单元,但这些是易失性存储器,当系统断电时,其内容会丢失。而且,当系统上电时,必须从外部来源(通常是闪存器件)加载配置数据。这些 FPGA 需要花费非常长的时间来完成上电和使用前的准备工作。

有些 FPGA 使用片上闪存来存储配置数据,但仍有基于 SRAM 的配置单元。在这种情况下,当上电时,片上控制器将配置数据从闪存配置存储器复制到 SRAM 配置单元。这些 FPGA 的上电速度比纯 SRAM 产品要快。

Microchip 的 IGLOO2 FPGA 和 SmartFusion2 SoC FPGA 采用不同的机制,片上配置存储器和片上配置单元均采用闪存技术实现。在 PolarFire 器件中,配置单元基于硅氧化氮氧化硅 (SONOS) 非易失性存储器 (NVM) 技术,可以将其视为“类似闪存,但更好”。

由于配置数据存储在非易失性闪存(或 SONOS)单元中,因此 Microchip 的 FPGA 和 SoC FPGA 可以“即时启动”。也就是说,它们的上电速度比任何其他类型的 FPGA 都要快。这些器件也包含闪存配置存储器的原因是,在将新配置加载到此配置中的同时,FPGA 可以使用其配置单元中的现有配置继续运行。一旦新配置下载完成并得到了验证(配置可以加密并附带循环冗余校验 (CRC)),便可将器件置于安全状态,同时使用配置存储器中存储的新配置覆盖配置单元中存储的原始配置。

传统器件:IGLOO2 FPGA

IGLOO2 是出色的综合型中低端 FPGA。许多设计人员认为这些器件是“传统”FPGA 器件。这些闪存 FPGA 器件非常适合执行通用功能,例如千兆位以太网或双 PCI Express 控制平面、桥接功能、输入/输出 (I/O) 扩展和转换、视频和图像处理、系统管理以及安全连接。应用范围非常广泛,包括通信、工业、医疗、国防和航空。

图 2:IGLOO2 FPGA 非常适合执行通用功能,例如千兆位以太网或双 PCI Express 控制平面、桥接功能、I/O 扩展和转换、视频和图像处理、系统管理以及安全连接。(图片来源:Microchip Technology)

图 2:IGLOO2 FPGA 非常适合执行通用功能,例如千兆位以太网或双 PCI Express 控制平面、桥接功能、I/O 扩展和转换、视频和图像处理、系统管理以及安全连接。(图片来源:Microchip Technology)

IGLOO2 FPGA 提供 5,000 至 150,000 个 LE(逻辑单元),具有高性能存储子系统、高达 512 KB 的嵌入式闪存、2 x 32 KB 的嵌入式静态随机存取存储器 (SRAM)、两个直接存储器访问 (DMA) 引擎以及两个双倍数据速率 (DDR) 控制器。这些器件还有多达 16 个收发器通道、集成 DSP 处理器块和抗/耐单粒子翻转 (SEU) 的存储器。为了安全起见,器件进行了差分功率分析 (DPA) 加固,并使用 AES256 和 SHA256 加密以及按需 NVM 数据完整性检查。

IGLOO2 器件的典型例子是 M2GL025-FGG484I,它有 27,696 个 LE、1,130,496 位 RAM 和 267 个 I/O。为使设计人员能够研究和试验 IGLOO2 FPGA 系列的特性,Microchip 还推出了相应的 IGLOO2 评估套件 M2GL-EVAL-KIT(图 3)。

图 3:M2GL-EVAL-KIT 是用于 IGLOO2 的评估套件,功能集成度高,具有低功耗、高可靠性、高级安全性等特性。(图片来源:Microchip Technology)

图 3:M2GL-EVAL-KIT 是用于 IGLOO2 的评估套件,功能集成度高,具有低功耗、高可靠性、高级安全性等特性。(图片来源:Microchip Technology)

M2GL-EVAL-KIT 有助于轻松开发嵌入式应用,涉及电机控制、系统管理、工业自动化和高速串行 I/O 应用、PCI Express 和千兆位以太网。该套件具有很高的功能集成度,并提供低功耗、高可靠性、高级安全性等特性。该板也采用小巧尺寸、兼容 PCIe 的结构,开发人员利用任何带有 PCIe 槽的台式 PC 或笔记本电脑即可进行原型设计。

入门级 SoC:SmartFusion2 SoC FPGA

SmartFusion2 SoC FPGA 基于 IGLOO2 器件的传统可编程结构,并增加了 32 位硬处理器核。由于该处理器是 Arm® Cortex® 系列的主打产品,因此 SmartFusion2 系列为进入 SoC FPGA 世界提供了一个很好的切入点。

这些 SoC FPGA 提供 5,000 至 150,000 个 LE 和一个 166 兆赫兹 (MHz) Arm Cortex-M3 处理器,并且包括嵌入式跟踪宏单元 (ETM) 和指令缓存并带有片上 eSRAM 与嵌入式 NVM (eNVM);还包括完整的微控制器子系统,并且配有 CAN、TSE、USB 等丰富的外设。

图 4:SmartFusion2 SoC FPGA 提供 5,000 至 150,000 个 LE 和一个 166 MHz Arm Cortex-M3 处理器,并且包括 ETM 和指令缓存并带有片上 eSRAM 与 eNVM;还包括完整的微控制器子系统,并且配有 CAN、TSE、USB 等丰富的外设。(图片来源:Microchip Technology)

图 4:SmartFusion2 SoC FPGA 提供 5,000 至 150,000 个 LE 和一个 166 MHz Arm Cortex-M3 处理器,并且包括 ETM 和指令缓存并带有片上 eSRAM 与 eNVM;还包括完整的微控制器子系统,并且配有 CAN、TSE、USB 等丰富的外设。(图片来源:Microchip Technology)

这些闪存 SoC FPGA 器件非常适合执行通用功能,例如千兆位以太网或双 PCI Express 控制平面、桥接功能、I/O 扩展和转换、视频和图像处理、系统管理以及安全连接。应用范围同样很广,包括通信、工业、医疗、国防和航空。

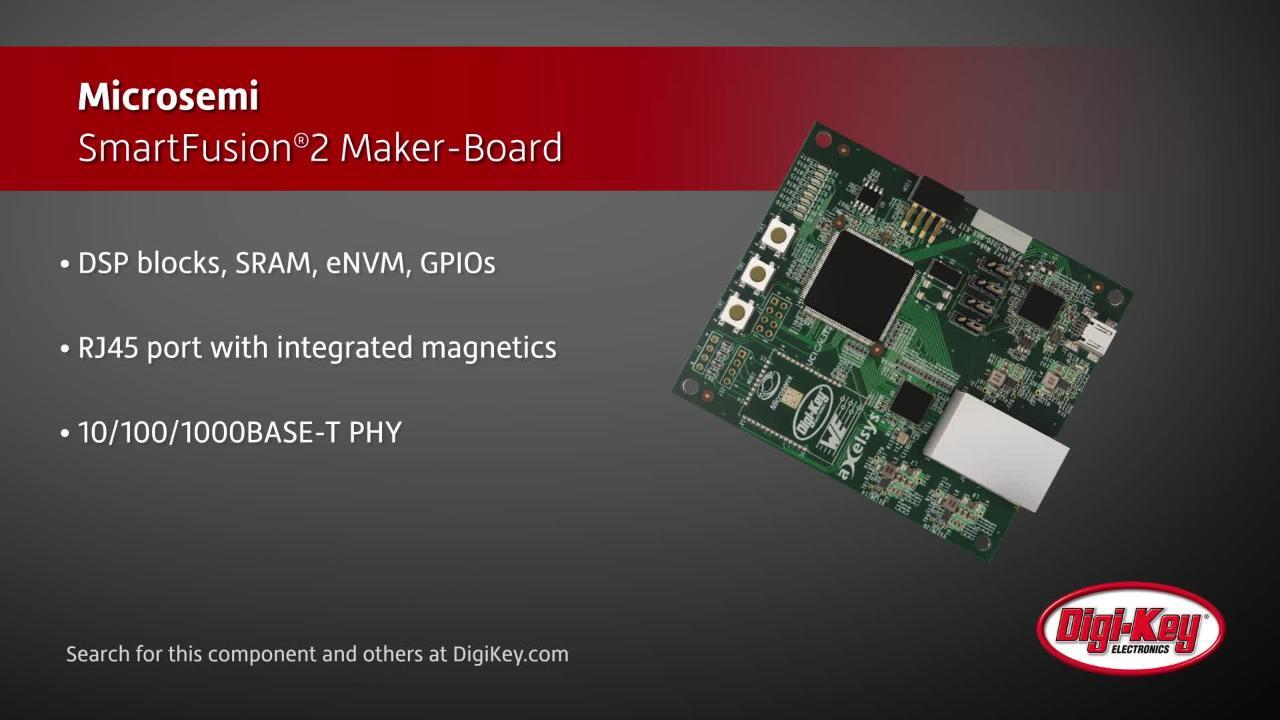

SmartFusion2 器件的典型例子是 M2S025-FCSG325I,它有 25,000 个 LE、256 KB 闪存、64 KB RAM 和一个 166 MHz 32 位 Arm Cortex-M3 处理器子系统。为使设计人员能够研究和试验 SmartFusion2 SoC FPGA 系列的特性,Microchip 还推出了相应的 SmartFusion2 创客开发板 M2S010-MKR-KIT(图 5)。

图 5:SmartFusion2 创客开发板是用于 SmartFusion2 SoC FPGA 的低成本评估套件,它将 Arm Cortex-M3 处理器与基于闪存的 FPGA 结构结合在一个芯片上,另有许多由 SoC 用户惯常使用的外设,例如 RAM 和 DSP 块。(图片来源:Microchip Technology)

图 5:SmartFusion2 创客开发板是用于 SmartFusion2 SoC FPGA 的低成本评估套件,它将 Arm Cortex-M3 处理器与基于闪存的 FPGA 结构结合在一个芯片上,另有许多由 SoC 用户惯常使用的外设,例如 RAM 和 DSP 块。(图片来源:Microchip Technology)

低成本 SmartFusion2 创客开发板由 DigiKey 独家销售,为设计人员使用 SmartFusion2 系列提供了便利。这一特别的设备提供了一个基于闪存的 FPGA 架构,具有 12,000 个 LE、一个 32 位 166 MHz Arm Cortex-M3 处理器、DSP 块、SRAM、eNVM 和 GPIO 接口,所有元件全都集成在单个芯片上。

SmartFusion2 创客开发板附加了以太网接口、环境光传感器、SPI 闪存、八个用户 LED 和两个用户按钮。该板还有两个无载但已布局好的连接,支持 ESP32 和 ESP8266 Wi-Fi/蓝牙模块(不包括在内)。它支持通过 USB 端口进行 JTAG 编程、UART 通信和为电路板供电。此外,该板还有 SPI 闪存、50 MHz 时钟源和 Microchip 的 VSC8541 物理层 (PHY),后者支持 100 Mbps 或 1 Gbps 以太网。

成本优化的高性能器件:PolarFire FPGA 和 SoC FPGA

PolarFire FPGA 是成本经过优化且采用 28 nm 工艺技术实现的高性能器件。这些器件提供中等密度,但功耗最低,并具有高度的安全性和可靠性。

该产品系列涵盖 100,000 到 500,000 个 LE,具有 12.7 Gb 收发器,设计功耗最多比同类中端 FPGA 低 50%。这些器件非常适合有线接入网络和蜂窝基础设施、国防和商业航空航天市场以及工业自动化和物联网市场中的广泛应用。

图 6:PolarFire FPGA 具有 100,000 到 500,000 个 LE 和 12.7 Gb 收发器,设计功耗最多比同类中端 FPGA 低 50%。(图片来源:Microchip Technology)

图 6:PolarFire FPGA 具有 100,000 到 500,000 个 LE 和 12.7 Gb 收发器,设计功耗最多比同类中端 FPGA 低 50%。(图片来源:Microchip Technology)

PolarFire FPGA 的总功耗比同类 FPGA 降低多达 50% 的主要原因是,片上配置存储器和片上配置单元均采用 NVM 技术。这使得配置单元之间的漏电流非常低。另外,这也意味着这些器件在上电时也能真正地“即时启动”,从而不会产生浪涌电流,配置电流也为零。

网络安全是网络边缘互连器件的首要考虑因素,因此对于开发人员而言,仅满足设计的功能要求是不够的,还要确保安全。安全性始于芯片制造,并一直持续到系统部署和运行。Microchip 推出的 PolarFire FPGA 是业界最先进的安全可编程 FPGA。

许多针对复杂电子设备的应用在设计中都有一定程度的安全要求。PolarFire FPGA 专为高可靠性、高可用性的安全和任务关键型系统而设计,适用于工业、航空、军事、通信等应用。PolarFire 之所以适合这些应用,是因为具有如下特性:

- 零失效率 (FIT) FPGA 配置

- 抗 SEU 存储器

- 具有单错误纠正、双错误检测 (SECDED) 功能的存储控制器

- 内置自检

- 无需外部配置器件

PolarFire 器件的典型例子是 MPF100T-FCSG325I,它有 109,000 个 LE、7,782,400 位 RAM 和 170 个 I/O。为使设计人员能够研究和试验 PolarFire FPGA 系列的特性,Microchip 还推出了相应的 PolarFire FPGA 评估套件 MPF300-EVAL-KIT(图 7)。

图 7:为使设计人员能够研究和试验 PolarFire FPGA 系列的特性,Microchip 还推出了相应的 MPF300-EVAL-KIT FPGA 评估套件。(图片来源:Microchip Technology)

图 7:为使设计人员能够研究和试验 PolarFire FPGA 系列的特性,Microchip 还推出了相应的 MPF300-EVAL-KIT FPGA 评估套件。(图片来源:Microchip Technology)

MPF300-EVAL-KIT 可针对各类应用提供高性能评估。它非常适合用于高速收发器评估、10 Gb 以太网、IEEE1588、JESD204B、SyncE、CPRI 以及其他应用。套件连接包括高引脚数 (HPC) FPGA 夹层卡 (FMC)、大量 SMA、PCIe、双千兆位以太网 RJ45、SFP+ 和 USB。PolarFire FPGA 具有 300,000 个 LE、DDR4、DDR3 和 SPI 闪存,可用于开发广泛的高性能设计。

PolarFire 产品线仍在进一步发展。在撰写本文时,Microchip Technology 披露了有关即将推出的 PolarFire SoC FPGA 系列的详细信息。该系列将拥有经过强化且支持 Linux、基于开源 64 位 RISC-V 的实时微处理器子系统。

使用 Microchip Technology 的 FPGA 进行设计与开发

最常用的 FPGA 开发技术之一是语言驱动设计 (LDD)。这涉及使用 Verilog、VHDL 或 SystemVerilog 等硬件描述语言 (HDL),在抽象级别(即寄存器传送级 (RTL))上捕获设计意图。通过逻辑仿真进行验证之后,该表达式将连同目标 FPGA 类型、引脚分配和时序约束(例如最大输入到输出延迟)等其他信息一并传输至合成引擎。合成引擎输出配置文件,对于 Microchip FPGA 或 SoC FPGA,配置文件直接加载到 FPGA 中,而对基于 SRAM 的器件而言,配置文件则是加载到外部存储器件中(图 6)。

图 8:通过逻辑仿真进行验证之后,RTL 设计描述将与 FPGA 类型、引脚分配和时序约束等其他设计细节一并传输至合成引擎。合成引擎输出的配置文件直接加载到 FPGA 中。(图片来源:Max Maxfield)

图 8:通过逻辑仿真进行验证之后,RTL 设计描述将与 FPGA 类型、引脚分配和时序约束等其他设计细节一并传输至合成引擎。合成引擎输出的配置文件直接加载到 FPGA 中。(图片来源:Max Maxfield)

Microchip 的 Libero SoC 设计套件属于此类工具。该软件提供了一套全面的易学易用的集成开发工具,支持使用 Microchip 的 IGLOO2 和 PolarFire FPGA 以及 SmartFusion2 和 PolarFire SoC FPGA 进行设计。该套件将行业标准 Synopsys Synplify Pro 综合、Mentor Graphics 的 ModelSim 仿真与约束管理、编程和调试工具、安全生产编程支持集成在一起。

除了使用 Verilog、VHDL 或 SystemVerilog 以文本格式捕获设计之外,该套件还包含图形输入功能,可以将系统定义为连接块的层次结构,较低级的块以用户定义的 HDL 或第三方 IP 表示。

另外,还有 System Builder,它是一种易于使用的设计工具,可引导用户解决一系列高级问题来定义目标系统。System Builder 首先询问有关目标系统架构的问题,然后添加需要在可编程结构中作为软内核实现的所有其他外设,最后创建一个“设计即正确”的完整系统。

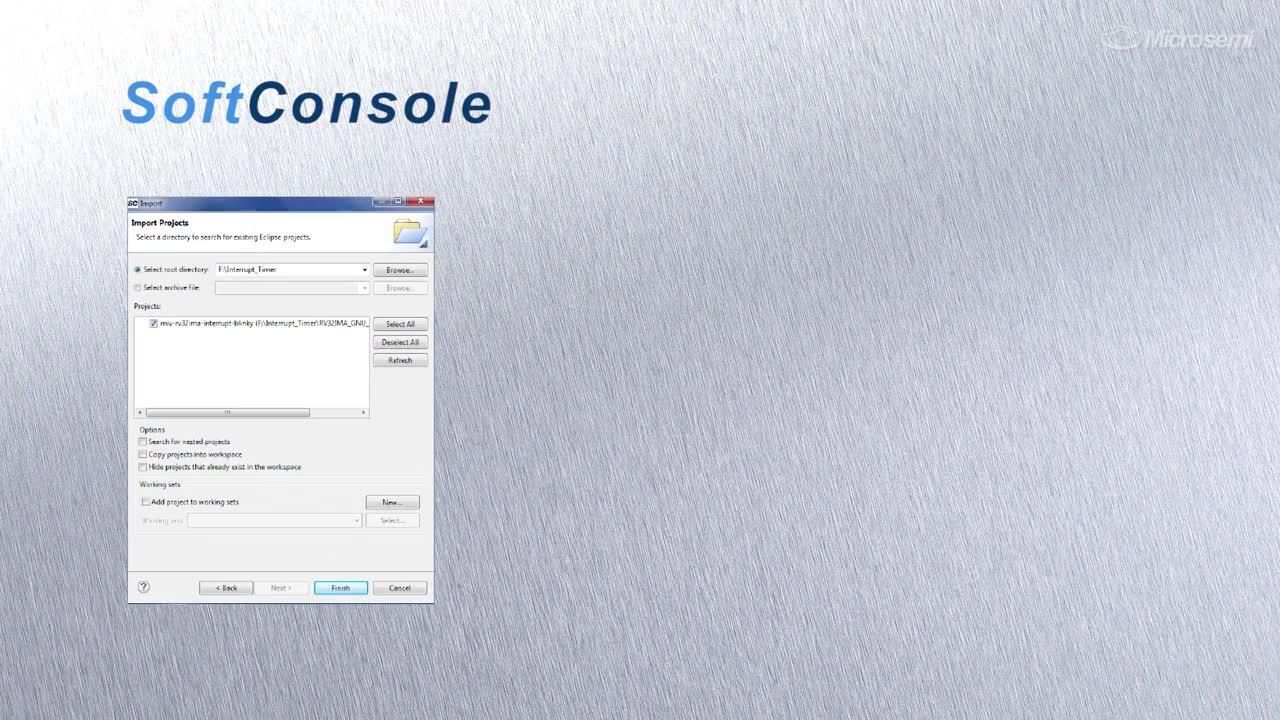

最后但并非最不重要的一点是 SoftConsole 集成开发环境 (IDE);对于 Microchip 的 FPGA 和 SoC FPGA 中实例化的 32 位软处理器,以及 SmartFusion2 和 PolarFire SoC FPGA 中的 32 位和 64 位硬处理器内核来说,该 IDE 有利于快速开发裸机和基于 RTOS 的 C/C++ 软件。

总结

最佳处理设计解决方案常常是由处理器与 FPGA 的组合提供,或由 FPGA 单独提供,或以硬处理器内核作为部分结构的 FPGA 提供。作为一项技术,FPGA 多年来发展迅速,能够满足灵活性、处理速度、功耗等多方面的设计需求,非常适合智能接口、机器视觉和 AI 等众多应用。

如本文所述,Microchip Technology 的 FPGA 和 SoC FPGA 产品范围覆盖中低端,以具有优异可靠性的低功耗、高安全性器件为主。这些 FPGA 具有强大的信号处理和存储器资源,是在通信、工业、军事、航空等行业中开发硬件加速、人工智能、图像处理、边缘计算等应用的出色平台。

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。