Merging MCU and DSP Functionality for Block- and Stream-Based Processing

投稿人:电子产品

2014-08-14

Microcontrollers do a good job of controlling our user interfaces. They can initialize other circuitry, monitor inputs, react to interrupts, and drive outputs for displays and controls. However, while on-chip analog functionality like A/D converters and D/A converters, PWMs, voltage references, op amps, and comparators lets an MCU function in the analog realm—and this is common for many relatively simple analog processing tasks—on the whole, microcontrollers are typically weak when it comes to processing analog signals.

A thermostat is a good example that virtually any mixed-signal microcontroller can handle. It monitors a temperature, compares it to a set point, and throws a switch. You can add programmed hysteresis, timed operations, cloud, and worldwide connectivity to it, but the bottom line is that the MCU throws or releases a switch to perform its task.

In the real world, however, most control loops operate much faster than a room’s temperature change, and monitor more than just one input. This is where basic attributes such as speed, performance, and flexible architecture are important, but also important is the type of DSP functionality either merged into the core of the microcontroller, or, sitting side by side with a microcontroller to tackle analog functionality, especially with block- or stream-oriented types of processing needs.

This article looks at levels of DSP functionality available in standard microcontrollers, as well as the features used to turn analog-signal processing into digital-domain solutions. All parts, datasheets, tutorials, and development kits referenced here can be found online at DigiKey’s website.

Processing approaches

Certain aspects of mixed-signal design are better served through clever partitioning of functionality as opposed to putting all the heavy lifting on a single control block. The two approaches are to capture raw data and do all processing in the digital world versus some rudimentary processing before the signal gets to the A/D. If processing resources are ample, then the simplest approach is to extract everything in raw form and take it from there.

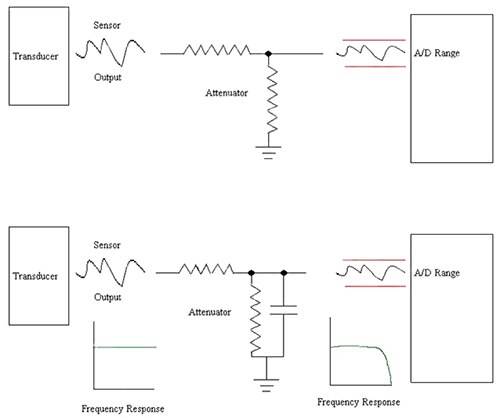

Most linear signals will need to run through some external components to match the range of the signal with the range of the A/D converters. This maximizes the dynamic range of data providing the highest resolution. Weak signals will need amplification, and powerful signals will need attenuation. If we can do some simple processing in the analog world before a signal gets into the A/D converters, we can reduce the amount of processing power needed depending on the algorithms the processor is running (Figure 1).

Figure 1: As long as an attenuator (top) is needed to place a signal within permissible voltage ranges, the addition of a simple capacitor (bottom) can turn the attenuator into a filter. This can reduce the amount of processing steps later on.

This is a simple case that shows how the addition of a single capacitor turns the attenuator into a low-pass filter. The point is that a balanced approach to hardware-based signal processing can cost very little extra, take up very little additional space, and simplify the design further up the road.

While filtering may still need to be performed in the digital realm, you may be able to reduce the amount of processing needed and lower cost, save energy, and reduce code development by cleverly partitioning functionality.

Levels of DSP

While in digital form, high-, low- and band-pass and notch filters can be continuously implemented in precise digital form as the filter processes the input waveforms. The same holds true for gain, inversion, attenuation, averaging, peak detection, low detection, integration, differentiation, and so on.

Once data is inside the processor, then the specifics of the processor type, architecture, speed, and special features determine whether it is suitable or not for the task at hand. While older Von Neumann CISC architectures are fine for simple control tasks, they are not ideal when it comes to mixed-signal functionality, especially when real-time aspects are introduced. A limitation is that with a CISC machine different types of instructions can use different numbers of cycles with multiple clock cycles per instruction. The efficacy of the code now depends on what instructions you use and where. Interrupt responses can also affect real-time performances.

Harvard architectures that use RISC are more streamlined for steady pipeline processing of streams of data. These typically execute in a single clock cycle or single-instruction cycle. RISC machines typically clock at much higher speeds, adding another performance-boost feature. A nice benefit for system designers is that data areas are separated from code space. This leaves more flexibility when partitioning and using memory blocks for captured data processing and scratchpad RAM.

The key in deciding which processor to throw at a mixed-signal task is the instruction set, especially fast multiply, multiply and accumulate, and fast division. Fixed- or floating-point requirements also weigh in here. These are particularly important with filters and analog-processing blocks that implement algorithms, especially if they need to solve algebraic and quadratic equations in real time.

Several processor cores add a multiply instruction or two and throw their hats in the ring as having DSP functionality. Still others are dedicated to signal processing, such as the Texas Instruments TMS320Cx family of processors. Not every DSP-capable processor has a full 32-bit architecture and screams at hundreds of MHz. Many applications do just fine with 16-bit functionality with 32-bit extensions.

Take for example the TI 16 bit fixed-point, 64K TMS320LF240 controller that more resembles an older-style microcontroller core from a resources and performance point of view. As a member of the 3 to 3.6 V C2xx series, they run up to 40 MHz, feature 10-bit A/D converters, 13 I/O, and 40-MIPS performance (one instruction per clock cycle) and are ideally suited for office equipment, metering, appliances, and motor control to name a few applications. A nice feature is its on-chip EEPROM for easy setup parameters and calibration data.

Another family of 16-bit parts that straddle the line between general-purpose microcontrollers and DSPs are the dsPIC processors from Microchip. The supplier also combines regular processor architectures with DSP enhancements with several of its family members, such as the dsPIC30F, dsPIC33F, and the dsPIC33EP families.

Consider the DSPIC30F2011-30I/SO as a relatively small part which can target designs like sensor actuators as part of a control loop. Do not be fooled by the 12 Kbytes of Flash and small 18-pin packages. As a matter of fact, the scalability of performance (from 16 to 70 MIPS) coupled with the scalability of its program resources (from 4 to 512 Kbytes of Flash), package size (from 14 to 144 pins), and mixed-signal resolution (from 10- to 16-bit A/Ds and D/As) make this part a single architecture to learn for a wide range of performance needs.

This 2.5 to 5.5 V core has the look and feel of a microcontroller, but also has a single-cycle 16 x 16 MAC with 40-bit accumulators, fast DMA without cycle stealing, low-power modes including 10 nA deep sleep, and a free library of filter-design tools.

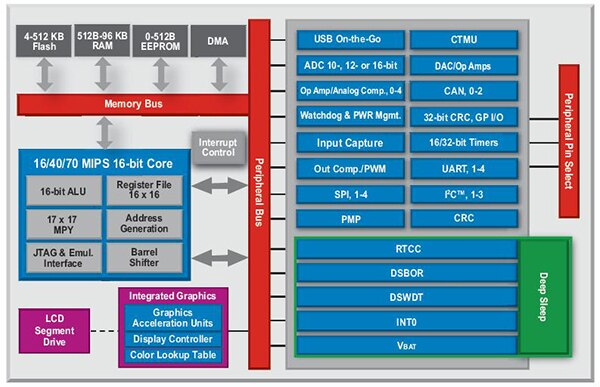

Bigger brothers like the DSPIC33EP512MU814-I/PH are perfect examples of larger 144- pin parts that blaze away at the full 70 MIPS throttle (Figure 2). A family overview Product Training Module on the PIC24EP 70-MIPS dsPIC33EP is available on the DigiKey website, as is an application Product Training Module example using these parts as motor controllers on a low voltage development board. Note: These parts also have EEPROM for run-time parameter store.

Figure 2: This 16-bit architecture resembles a microcontroller with added DSP functionality, memory resources, and a rich set of peripherals. The 10-, 12-, or 16-bit A/D converters, the on-chip op-amps, input and output capture and compare, and PWMs round out the mixed-signal capabilities of the 70 MIPS part.

On the 32-bit side TI offers a DaVinci Series of Dual Core processors that combine an ARM core along side a DSP core. Take for example the TMS320DM6446AZWT digital media system-on-a-chip. The fixed-point TMS320C64X co-processor system on module part has six ALUs and two multipliers and runs at 594 MHz. Flavors up to 810 MHz are available. The on-chip ARM926 core also has some DSP extensions and runs 297 MHz in this case, but can run up to 405 MHz in other family members.

In summary

The types of processor architectures, performance levels, peripheral mixes, and computational resources determine if a selected microcontroller is suitable for a real-time signal-intensive design. Block and stream processors that operate on continuously varying waveforms can keep up admirably when the right part is coupled with the most effective design partitioning at the top-down level of the design stage.

To help find the candidates that are best suited for the design, take advantage of well-implemented parametric search engines. Matching the right part to the right partitioned design can lower costs and speed up development cycles.

For more information on the parts discussed in this article, use the links provided to access product information pages on the DigiKey website.

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。