如何使用 SPXO 满足低功耗电路对功能简单且经济实惠的要求

投稿人:DigiKey 北美编辑

2021-08-25

电路计时是众多电子设备所需的关键功能,包括微控制器、USB、以太网、Wi-Fi 和蓝牙接口,以及计算设备和外围设备、医疗设备、测试和测量设备、工业控制和自动化、物联网 (IoT)、可穿戴设备和消费电子产品。通过设计晶体控制型振荡器来提供系统定时,起初似乎简单,但将石英晶体与振荡器 IC 匹配时设计者必须考虑许多参数和设计要求。

有许多需要考虑是因素,具体包括晶体运动阻抗、谐振模式、激励功率和振荡器负电阻。在电路布局方面,设计者需要考虑 PC 板的寄生电容,在晶体周围加入保护带以及片上集成电容。最终设计需要紧凑可靠,元件数量最少,具有较低的均方根 (rms) 抖动,并在较宽的输入电压范围内功耗最小。

简单封装的晶体振荡器 (SPXO) 是一种解决方案。这些连续电压振荡器针对低功耗和低 RMS 抖动进行了优化并可在 1.60 V 和 3.60 V 之间的任何电压下运行,这让设计者能够实现只需极少设计即可集成到系统中的解决方案。

本文将简要讨论一些在使用分立式石英晶体和定时 IC 顺利设计定时电路时,必须满足的重要性能要求和必须克服的设计挑战。然后介绍 Abracon 的 SPXO 解决方案,说明设计人员如何利用这些器件来切实有效地满足电子系统的定时需求。

晶体振荡器的运行和设计挑战

功耗是小型电池供电型无线设备的一个重要考虑因素。许多类似设备基于功耗极低的片上系统 (SoC) 无线电和处理器,可以支持连续数年的电池寿命。此外,由于电池可能是系统中最昂贵的部件,因此尽量减少电池的尺寸对控制设备成本非常重要。也就是说,待机电流往往是小型无线系统中最重要的电池寿命考虑因素,而待机电流往往由时钟振荡器主导。因此,至关重要好的一点就是尽量减少振荡器的电流消耗。

遗憾的是,设计低功耗振荡器可能是一个挑战。节省能源的一个方法是通过进入“禁用”状态并在需要时启动振荡器来尽量减少待机电流。然而,要求晶体振荡器快速、可靠地启动并非易事。设计者需要保证振荡器在待机时处于低电流状态,在所有工作和环境条件下具有可靠的启动特性。

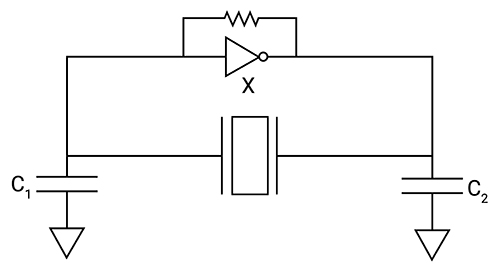

Pierce 振荡器的配置常见于低功耗无线 SoC 中(图 1)。Pierce 振荡器基于晶体 (X) 和负载电容(C1 和 C2)构建,由一个使用内部反馈电阻的反相放大器包围。在合适的条件下,当放大器的输出被反馈到输入端时,会产生负电阻并发生振荡。

图 1:围绕晶体 (X) 和负载电容 C1 和 C2 构建的基本 Pierce 振荡器配置。(图片来源:Abracon)

图 1:围绕晶体 (X) 和负载电容 C1 和 C2 构建的基本 Pierce 振荡器配置。(图片来源:Abracon)

晶体结构复杂;本讨论只关于在振荡器中运行的晶体的顶层和简化结构。

闭环增益余量 Gm 可以作为一个品质因数 (FOM) 来描述振荡器相对于各种损耗的可靠性。闭环增益余量也被称为振荡裕度 (OA)。OA 低于 5 时会导致生产吞吐量低以及与温度相关的启动问题。OA 值等于或高于 20 的设计稳健耐用,在设计工作温度范围内运行可靠,并且不同生产批次对晶体和 SoC 性能特征的影响极小。

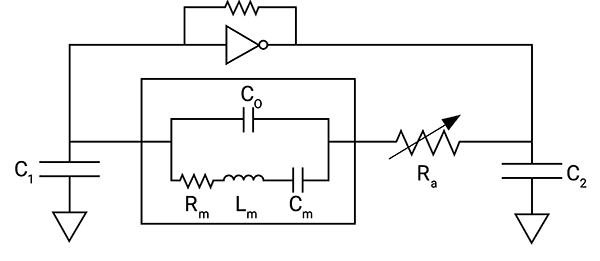

为了测量振荡器的 OA,可在电路中添加可变电阻 Ra(图 2)。增加 Ra 值,直到振荡器无法启动。这就是用来确定 OA 值的方法,如下所示:

![]() 等式 1

等式 1

其中:

Rn 是负电阻

Re 是等效串联电阻 (ESR)。

![]() 等式 2

等式 2

![]() 等式 3

等式 3

其中,负载电容 CL 的计算方法如下:

![]() 等式 4

等式 4

其中 Cs 是电路的可变电容器,电容值通常在 3.0 至 5.0 pF 之间。

图 2:显示了扩展晶体模型(中间方框)和用于测量振荡裕度的可调电阻器 (Ra)。(图片来源:Abracon)

图 2:显示了扩展晶体模型(中间方框)和用于测量振荡裕度的可调电阻器 (Ra)。(图片来源:Abracon)

OA 取决于 ESR (Re),而 ESR 则取决于石英晶体参数 Rm 和负载电容 CL。对于低功耗振荡器,如低功耗无线设备中使用的振荡器,Rm 和 CL 对 OA 的影响会增大。测量 OA 比较耗时,可能会延长开发过程。因此,该项工作可能被忽视,从而导致系统或设备投入生产时出现性能问题。

此外,通过设置高 OA 来确保振荡器可靠运行,会导致其他问题。例如,OA 越高振荡器电路性能越高,但可能会忽略由于晶体造成的功率损失。这种损耗可能是一个重要因素。再来看图 2,晶体运动电阻 Rm 在电流周期性流经电阻时造成功率耗散。当 CL 较大时,会增加电流和损耗。因此,设计者需要在晶体的功率损耗和合理的 OA 值之间取得平衡。

避免抖动

设计石英晶体振荡器时,了解和减少抖动是很重要的。抖动有两种类型,通常都以均方根值来衡量:

- 周期间 抖动:也叫相位抖动,是指几个被测量的振荡周期之间的最大时间差,通常至少测量 10 个周期。

- 周期 抖动:这是一个时钟沿的最大变化,需测量每个周期,而非多个周期。

石英晶体振荡器的主要抖动源包括电源噪声、信号频率的整数次谐波、不当的负载和端接条件、放大器噪声和某些电路配置。根据不同的来源,可采用不同的方法尽量减少抖动。

- 使用旁路电容、片式磁珠或电阻电容 (RC) 滤波器来控制电源噪声。

- 在要求极低抖动的关键应用中,建立一种控制谐波的方法至关重要(不再本文探讨范围)。

- 通过优化负载和端接条件,减少反射回输出的功率。

- 避免使用包含锁相环、乘法器或可编程功能的设计,因为它们往往会增加抖动。

连续电压晶体振荡器

使用 Abracon 的 ASADV、ASDDV 和 ASEDV SPXO,有利于设计偏置电压在 1.60 至3.60 V 之间变化的系统(图 3)。SPXO 系列涵盖不同的频率范围;ASADV 器件的频率为 1.25 MHz 至 100 MHz,ASDDV 和 ASEDV 器件的频率为 1MHz 至 160MHz。该系列均符合 RoHS/RoHS II 标准,采用密封式陶瓷表面贴装器件 (SMD) 封装。在 -40°C 至 +85°C 的工作温度范围内,该系列频率稳定性为 ±25ppm。

图 3:ASADV(如图所示)、ASDDV 和 ASEDV SPXO 采用密封式陶瓷封装,工作温度范围为 -40℃ 至 +85℃。(图片来源:Abracon)

图 3:ASADV(如图所示)、ASDDV 和 ASEDV SPXO 采用密封式陶瓷封装,工作温度范围为 -40℃ 至 +85℃。(图片来源:Abracon)

ASADV 的尺寸为 2.0 x 1.6 x 0.8 mm,ASDDV 的尺寸为 2.5 x 2.0 x 0.95 mm,ASEDV 尺寸为 3.2 x 2.5 x 1.2 mm。这三个系列可在各种常见的工作温度范围内工作,提供多种稳定性选择以及兼容 CMOS/HCMOS/LVCMOS 的输出格式。

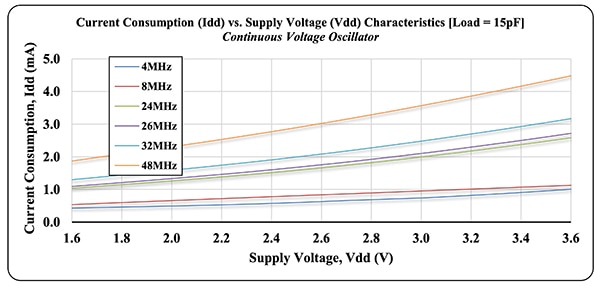

重要的是,ASADV、ASDVD 和 ASEDV 系列针对低电流运行进行了优化(图 4)。输出启用/禁用功能在禁用时电流降低至只有 10 μA。这些器件的最大启动时间为 10 ms。

图 4:ASEDV 的电流消耗与电源电压的关系,这是该 SPXO 家族器件的典型性能(在 25℃±3℃ 下测量)。(图片来源:Abracon)

图 4:ASEDV 的电流消耗与电源电压的关系,这是该 SPXO 家族器件的典型性能(在 25℃±3℃ 下测量)。(图片来源:Abracon)

所有三个系列的 SPXO 都具有特别低的电流消耗。对于 ASADV,在 25°C 温度下对 15 pF 负载进行测量时,最大电流范围为从 1.25 MHz 和 1.8 V 电源电压下的 1.0 mA,到 81 MHz 和 3.3 V 电源电压下的 14.5 mA。对于 ASDDV 和 ASEDV,最大电流范围为从 1 MHz 和 1.8 V 电源电压下的 1.0 mA,到 157 MHz 和 3.3 V 电源电压下的 19 mA。

这些器件可以驱动多个负载,具有良好的电磁干扰 (EMI) 性能和低抖动性能。这些器件的均方根相位抖动 <1.0 ps,最大周期抖动为 7.0 ps。

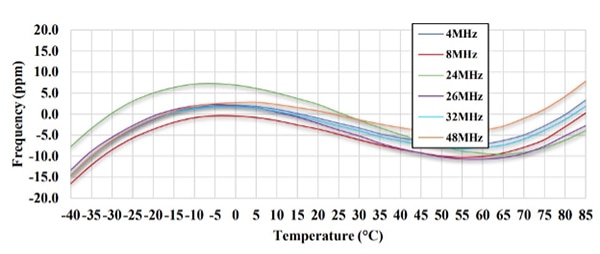

SPXO 在整个工作温度范围内也具有良好的频率稳定性(图 5)。在许多应用中,这些振荡器可以作为即插即用型解决方案,不需要任何设计工作。有了这些振荡器,无需选择偏置特定性振荡器,并消除了与偏置有关的频率变化。

图 5:这些 SPXO 在整个工作温度范围内具有良好的频率稳定性。该图是 ASEDV 系列的典型图。(图片来源:Abracon)

图 5:这些 SPXO 在整个工作温度范围内具有良好的频率稳定性。该图是 ASEDV 系列的典型图。(图片来源:Abracon)

最后,当冲击和振动不是关键考虑因素时,ASADV、ASDVD 和 ASEDV 连续电压表面贴装晶体振荡器可用于微机电系统 (MEMS) 振荡器的低成本替代品。

总结

设计者需要精确和可靠的振荡器,以便在广泛的应用和工作温度范围内提供稳定的定时。分立式晶体控制振荡器可以满足所需的性能特征,但在技术上很难做到有效地使用晶体进行设计,并耗时并造成不必要的成本。此外,在外形尺寸方面也不是最优选择。

如图所示,设计者可以使用低功耗集成 SPXO。这种 SPXO 形成了即用型计时解决方案,在很宽的工作温度范围内实现了优良的的频率稳定性。使用 SPXO,设计者可以减少元件数量,缩小解决方案尺寸,降低装配成本并提高可靠性。

推荐阅读

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。

中国

中国