如何在降低成本的同时让能源基础设施更加高效和可靠

投稿人:DigiKey 北美编辑

2022-03-30

从电动汽车 (EV) 充电站和太阳能逆变器到能源储存和不间断电源系统,能源基础设施的设计人员持续面临着减少碳排放量、提高可靠性和降低成本的挑战。

为了实现这些目标,他们需要仔细研究如何优化其电源转换解决方案,以减少传导和开关损耗,保持良好的热性能,减少整体外形尺寸,并降低电磁干扰 (EMI)。他们还必须确保所选择的解决方案能够满足生产件批准程序 (PPAP),并符合 AEC-Q101 标准要求。

为了应对这些挑战,设计人员可以转而使用各种碳化硅 (SiC) 功率 MOSFET、SiC 肖特基二极管、栅极驱动器 IC 和电源模块。

本文简要回顾了与经典的硅 (Si) 方案相比,SiC 技术是如何提高效率和可靠性并降低成本的。然后在介绍 onsemi 的几个实际案例之前,先探讨了 SiC 的封装和系统集成选项,并展示了设计人员该如何最好地应用它们来优化 SiC 功率 MOSFET 和栅极驱动器性能,以应对能源基础设施的挑战。

SiC 与 Si

SiC 是一种宽带隙 (WBG) 材料,其带隙为 3.26 电子伏特 (eV),而 Si 的带隙为 1.12 eV。与 Si 相比,SiC 提供了 10 倍的击穿场能力,超过 3 倍的导热率,并且可以在更高的温度下工作。这些规格使得 SiC 很适合用于能源基础设施应用(表 1) 。

|

表 1:与 Si 相比,4H-SiC 的材料属性使之非常适合用于能源基础设施应用。(图片来源:Onsemi)

更高的击穿电场使得更薄的 SiC 器件具有与更厚的 Si 器件相同的额定电压,而且相应地的是,更薄的 SiC 器件就具有了更低的导通电阻和更高的电流能力。SiC 的迁移率参数与 Si 处于同一数量级,支持紧凑的外形尺寸,这两种材料都可用于高频功率转换。其更高的导热率意味着 SiC 器件在更高的电流水平下温升会更低。SiC 器件的工作温度受限于封装因素,如引线键合,而不是 SiC 材料特性。因此,选择最优封装样式才是设计人员使用 SiC 时重要考虑因素。

SiC 的材料特性使之成为许多高压、高速、大电流和高密度电源转换设计的绝佳选择。在许多情况下,问题不在于是否使用 SiC,而在于什么 SiC 封装技术能提供最佳的性能和成本取舍。

设计人员在使用 SiC 电源技术时有三种基本的封装选择:分立器件、智能电源模块 (IPM) 或电源集成模块 (PIM) ,每一种都有一套独特的成本和性能取舍(表 2)。例如:

- 当成本是一个主要考虑因素时,如消费应用,通常倾向于使用分立器件。此外它们还支持双源,并有很长的使用寿命。

- IPM 解决方案减少了设计时间,具有最高的可靠性,是最紧凑的中功率水平解决方案。

- 与 IPM 相比,PIM 可以支持更高的功率设计,具有更好的功率密度、合理的快速上市速度、广泛的设计选择,以及更多的实现双源的机会。

表 2:在选择分立、IPM 和 PIM SiC 封装解决方案时的集成特性和取舍之比较。(图片来源:Onsemi)

表 2:在选择分立、IPM 和 PIM SiC 封装解决方案时的集成特性和取舍之比较。(图片来源:Onsemi)

混合 Si/SiC IPM

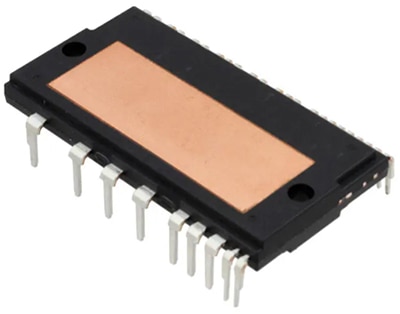

虽然有可能开发只使用 SiC 器件的解决方案,但有时使用 Si/SiC 混合设计更具有成本效益。例如,onsemi 的 NFL25065L4BT 混合 IPM 在输出端将第四代 Si IGBT 与 SiC 升压二极管组合在一起,形成一个交错式功率因数校正 (PFC) 输入级,适合用于消费、工业和医疗应用(图 1) 。这种紧凑的 IPM 包括了一个经过优化的 IGBT 栅极驱动,以尽可能减少 EMI 和损失。集成的保护功能包括欠压锁定、过流关断、热监控和故障报告。NFL25065L4BT 的其他特性包括:

- 600 伏/50 安培 (A) 两相交错式 PFC

- 针对 20 千赫 (kHz) 开关频率进行了优化

- 使用氧化铝直接键合铜 (DBC) 基底实现低热阻

- 集成用于温度监测的负温度系数 (NTC) 热敏电阻

- 隔离额定值达 2500 伏均方根 (rms)/1 分钟

- UL 认证

图 1:NFL25065L4BT IPM 在输出端使用第四代 Si IGBT 与 SiC 升压二极管组成交错式 PFC 级。(图片来源:Onsemi)

图 1:NFL25065L4BT IPM 在输出端使用第四代 Si IGBT 与 SiC 升压二极管组成交错式 PFC 级。(图片来源:Onsemi)

SiC PIM

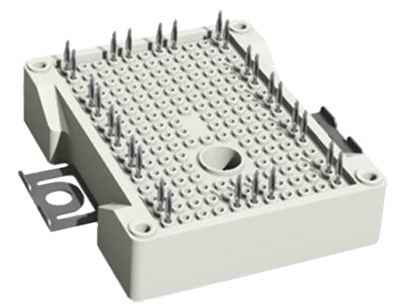

对于太阳能逆变器、电动汽车充电站和类似应用,如果能够使用基于 SiC 的 PIM,通过减少封装和缩小总体积来最大限度地提高功率传输,那么设计人员就可以转而使用 NXH006P120MNF2PTG。该器件包括一个 6 毫欧 (mΩ)、1200 伏的 SiC MOSFET 半桥和一个集成 NTC 热敏电阻,采用 F2 封装(图 2)。封装选项包括:

- 有或没有预涂热界面材料 (TIM)

- 可焊接引脚或压配引脚

图 2:NXH006P120MNF2PTG 集成电源模块采用 F2 封装,带有压配引脚。(图片来源:Onsemi)

图 2:NXH006P120MNF2PTG 集成电源模块采用 F2 封装,带有压配引脚。(图片来源:Onsemi)

这些 IPM 最大工作结温为 175 摄氏度 (°C),需要外部控制装置和栅极驱动器。可选的压配技术,也称为冷焊接,在引脚和印刷电路板上的电镀通孔之间提供可靠的连接。压配提供了简化的组装方式,无需焊接,可实现气密性、低电阻、金属对金属连接。

SiC 肖特基二极管

SiC 肖特基二极管可与 IPM 结合使用,或用于 100% 的分立设计,与 Si 二极管相比,它们具有更好的开关性能和更高的可靠性。像 1700 伏/25 A NDSH25170A 这样的 SiC 肖特基二极管,没有反向恢复电流,具有出色的热性能,以及与温度无关的开关特性。这些可转化为更高的效率、更快的开关频率、更高的功率密度、更低的电磁干扰和更轻松的并联,而所有这些都有助于减少解决方案的尺寸和成本(图 3)。NDSH25170A 的特性包括:

- 175°C 最大结温

- 506 毫焦耳 (mJ) 雪崩额定值

- 最高 220 A 的非重复性浪涌电流,最高 66 A 的重复性浪涌电流

- 正温度系数

- 无反向恢复,也无正向恢复

- AEC-Q101 认证资质/PPAP 能力

图 3:1700 伏/25 A NDSH25170A SiC 肖特基二极管没有反向恢复电流,具有出色的热性能,以及与温度无关的开关特性。(图片来源:Onsemi)

图 3:1700 伏/25 A NDSH25170A SiC 肖特基二极管没有反向恢复电流,具有出色的热性能,以及与温度无关的开关特性。(图片来源:Onsemi)

分立式 SiC MOSFET

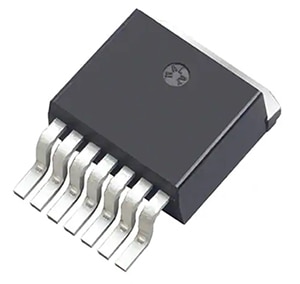

设计人员可以将分立式 SiC 肖特基与 onsemi 的 1200 V SiC MOSFET 结合在一起,与 Si 器件相比,SiC MOSFET 还具有优异的开关性能、更低的导通电阻和更高的可靠性。SiC MOSFET 的紧凑芯片尺寸获得了低电容和栅极电荷。较低的电容和栅极电荷加上低导通电阻,有助于提高系统效率,实现更快的开关频率,提高功率密度,降低电磁干扰 (EMI),并允许更小的解决方案外形尺寸。例如,NTBG040N120SC1 的额定电压为 1200 伏,电流为 60 安,采用 D2PAK−7L 表面贴装封装(图 4)。特性包括:

- 106 纳库仑 (nC) 典型栅极电荷

- 139 皮法拉 (pF) 典型输出电容

- 100% 雪崩测试

- 175°C 工作结温

- AEC-Q101 鉴定

图 4:NTBG040N120SC1 SiC MOSFET 的额定值为 1200 伏/60 A,导通电阻为 40 mΩ,采用 D2PAK−7L 表面贴装封装。(图片来源:Onsemi)

图 4:NTBG040N120SC1 SiC MOSFET 的额定值为 1200 伏/60 A,导通电阻为 40 mΩ,采用 D2PAK−7L 表面贴装封装。(图片来源:Onsemi)

SiC MOSFET 栅极驱动器

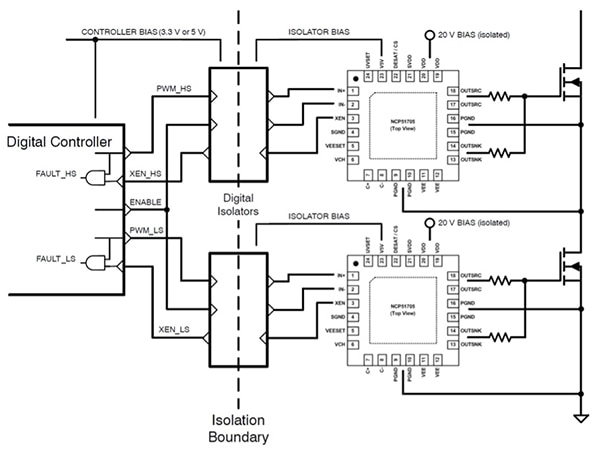

用于 SiC MOSFET 的栅极驱动器,如 onsemi NCx51705 系列,提供的驱动电压比用于 Si MOSFET 的驱动器高。全导通 SiC MOSFET 需要 18 至 20 伏的栅极电压,而导通 Si MOSFET 则需要不到 10 伏的电压。此外,SiC MOSFET 在关断时需要 -3 至 -5 伏的栅极驱动。设计人员可以使用针对 SiC MOSFET 优化的 NCP51705MNTXG 低压侧、单 6 A 高速驱动器(图 5)。NCP51705MNTXG 提供了最大的额定驱动电压,以实现低传导损耗,并且在导通和关断期间提供高峰值电流,以尽量减少开关损耗。

图 5:简化示意图显示两个 NCP51705MNTXG 驱动器 IC(中右)以半桥拓扑结构驱动两个 SiC MOSFET(右)。(图片来源:Onsemi)

图 5:简化示意图显示两个 NCP51705MNTXG 驱动器 IC(中右)以半桥拓扑结构驱动两个 SiC MOSFET(右)。(图片来源:Onsemi)

设计人员可以使用集成充电泵来产生用户可选择的负电压轨,以提供更高的 可靠性、提升的 dv/dt 抗扰度以及更快的关断速度。在隔离设计中,可以用一个从外部获得的 5 伏电压轨为数字或高速光隔离器的二次侧供电。NCP51705MNTXG 的保护功能包括基于驱动电路结温的热关断,以及偏置电源欠压锁定监控。

评估板和 SiC 栅极驱动注意事项

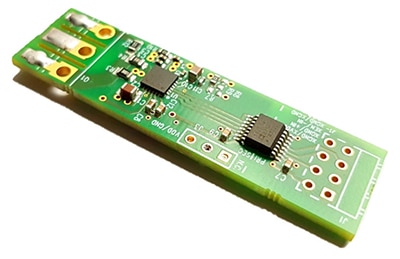

为了加快评估和设计过程,设计人员可以使用 NCP51705SMDGEVB 评估板 (EVB) 来评估 NCP51705(图 6)。该评估板包括一个 NCP51705 驱动器和所有必要的驱动电路,包括一个板载数字隔离器以及能够焊接任何采用 TO−247 封装的 SiC 或 Si MOSFET。该评估板旨在用于任何低压侧或高压侧的电源开关应用。在图腾柱驱动器中可以配置两个或多个这样的评估板。

图 6:NCP51705SMDGEVB EVB 有孔(上左),可连接 SiC 或 Si 功率 MOSFET,且包括 NCP51705 驱动器(U1,中左)和数字隔离器 IC(右中)。(图片来源:Onsemi)

图 6:NCP51705SMDGEVB EVB 有孔(上左),可连接 SiC 或 Si 功率 MOSFET,且包括 NCP51705 驱动器(U1,中左)和数字隔离器 IC(右中)。(图片来源:Onsemi)

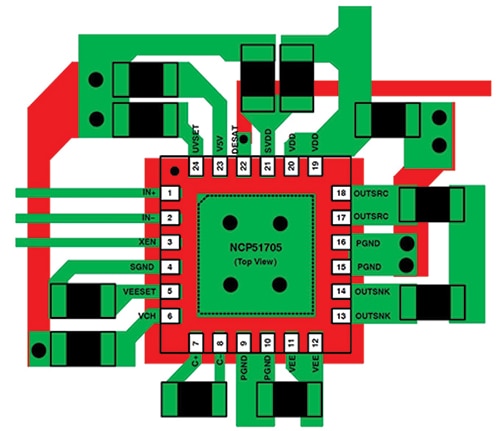

在使用带有 SiC MOSFET 的 NCP51705 栅极驱动器时,尽量减少印刷电路板的寄生电感和电容是很重要的(图 7)。印刷电路板布局注意事项:

- NCP51705 应尽可能靠近 SiC MOSFET,要特别注意的是 VDD、SVDD、V5V、充电泵和 VEE 电容与 MOSFET 之间的短印制线。

- VEE 和 PGND 之间的印制线应尽可能短。

- 高 dV/dt 印制线与驱动器输入和 DESAT 之间需要有隔离,以避免因噪声耦合而导致的异常操作。

- 对于高温设计,应在裸焊盘和外层之间使用热过孔,以尽量减少热阻。

- OUTSRC、OUTSNK 和 VEE 需要使用宽印制线。

图 7:NCP51705 的推荐印刷电路板布局,可最大程度地减少驱动 SiC MOSFET 的寄生电感和电容。(图片来源:Onsemi)

图 7:NCP51705 的推荐印刷电路板布局,可最大程度地减少驱动 SiC MOSFET 的寄生电感和电容。(图片来源:Onsemi)

结语

SiC 在帮助设计人员满足数量和种类日益增长的能源基础设施应用的需求方面发挥着重要作用。设计人员现在可以使用 SiC 器件设计更有效的高压、高速、大电流电源转换设计,从而获得更小的解决方案尺寸和更高的功率密度。但是为了让 SiC 设计获得最大收益,选择最佳的封装方式是很重要的。

如上所述,在分立器件、IPM 和 PIM 之间进行选择时,需要考虑一系列的性能、上市速度和成本权衡。此外,在使用分立器件或 PIM 时,为了实现可靠和高效的系统性能,SiC 栅极驱动器的选择和最佳的印刷电路板布局也至关重要。

推荐阅读

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。

中国

中国