加速网络性能:RDMA 对融合以太网 (RoCE) 的影响

2024-12-27

计算密集型应用的快速发展,凸显了对更快、更高效和可扩展网络解决方案的需求。 为满足这一需求而出现的最具创新性的技术包括了 RoCE 技术,即通过融合以太网远程直接内存访问 (RDMA) 。 这项开创性的技术有助于系统间的直接数据传输,无需 CPU 干预,显著减小了延迟并提高了系统的整体性能。 著名的 FPGA 设计公司 iWave 走在了这一技术进步的前沿,通过将 AMD 的 ERNIC IP(以太网 RDMA 网络接口控制器知识产权)集成到其嵌入式计算模块产品组合中,实现了强大的 100G 以太网解决方案。 这一整合将提升高性能应用中的 RDMA 功能。

图 1:RoCE 有助于系统间的直接数据传输,无需 CPU 干预,从而显著减小延迟并提高系统整体性能。(图片来源:iWave)

图 1:RoCE 有助于系统间的直接数据传输,无需 CPU 干预,从而显著减小延迟并提高系统整体性能。(图片来源:iWave)

了解融合以太网 RDMA (RoCE)

RDMA 是一项关键技术,可实现主机或服务器之间的直接内存传输,有效绕过 CPU。 这种功能可使 CPU 专注于执行应用和处理数据,从而显著提高网络性能,包括减小延迟、降低 CPU 负载和增加带宽,所有这些都具有成本效益。 RoCE 是一种特定的网络协议,旨在促进通过太网网络的 RDMA 运行。 通过利用现有的以太网基础设施,RoCE 为那些希望在不彻底改造现有网络设置的情况下提高性能的企业提供了一种极具吸引力的选择。

RoCE 的类型

根据所使用的网络适配器,RoCE 分为两个不同的版本:RoCE v1 和 RoCE v2。

- RoCE v1:该协议允许位于同一以太网广播域 (VLAN) 内的两台主机进行通信。 该协议使用 0x8915 以太类型,将标准以太网帧限制为 1500 字节,同时允许以太网巨型帧扩展至 9000 字节。

- RoCE v2:针对 RoCE v1 的局限性,RoCE v2 通过引入了 IP 和 UDP 报头,增强了数据包封装功能。 这一修改使 RoCE v2 能够横跨第 2 层(数据链路层)和第 3 层(网络层)网络实现无缝运行,从而支持第 3 层路由和跨多个子网的可扩展性。 RoCE v2 通常被称为可路由 RoCE (RRoCE),还增加了对 IP 组播的支持,进一步拓宽了其适用范围。

ERNIC IP:增强 RDMA 功能

ERNIC(支持嵌入式 RDMA 的 NIC)IP 是一种可定制的以太网 RDMA 网络接口控制器 IP 核,专为与 AMD FPGA、MPSoC 和软 MAC IP 实现无缝集成而设计。 该解决方案的特点是吞吐量大、低延迟,以及通过标准以太网提供完全硬件卸载的、可靠的数据传输机制。 iWave 成功实施了 100G 以太网解决方案,体现了其对技术进步的承诺。 这一成就得益于 iWave 的 Zynq UltraScale+ MPSoC 开发套件,该套件集成了 AMD 的 ERNIC IP。

Zynq UltraScale+ MPSoC 开发套件采用高速 QSFP-28 连接器,专为 100G 以太网解决方案的原型开发和评估而定制。

演示设置

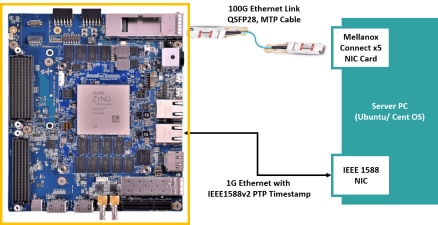

典型的演示装置(图 2)包括:

- iWave 的 Zynq UltraScale+ MPSoC ZU19EG 驱动型开发套件

- Advantech Mellanox ConnectX-5 100G 网卡

- 启用同步 1588 PTP 的 1G 网卡

- MTP 电缆、QSFP-28 模块和 CAT6 RJ45 以太网电缆

- Ubuntu 22.04 服务器 PC

图 2:Zynq UltraScale+ MPSoC 开发套件的典型设置。(图片来源:iWave)

图 2:Zynq UltraScale+ MPSoC 开发套件的典型设置。(图片来源:iWave)

系统架构概览

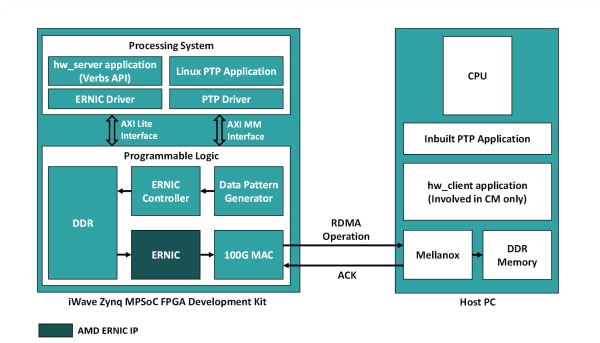

系统架构旨在优化数据传输,并明确界定处理系统 (PS) 和可编程逻辑 (PL) 组件的作用。 该系统还具有精确时间协议 (PTP) 同步功能,这对实时应用至关重要。 该技术具有卓越的性能指标,例如能够以每秒 100 帧以上的速度处理 8K 视频,其潜在应用领域涵盖数据中心、多媒体和高性能计算等众多领域,突显了该技术在现代计算环境中的多功能性和重要性。

图 3 所示的系统高层架构突出了 PS 和 PL 组件在 Zynq UltraScale+ MPSoC 中的不同作用。 PS 采用基于 ARM Cortex-A53 的 Hard SoC,对于系统配置、控制和诊断至关重要。 该架构的主要组成部分包括:

- 100G 以太网 MAC 驱动:确保实现在 100 Gb/s 速度下的稳健运行和低延迟数据传输

- ERNIC 控制器驱动:负责管理传入 DDR 的数据,并通过有效的门铃交换来促进用户应用与 ERNIC IP 之间的通信

- RDMA 内核和用户空间库:确保 RDMA 运行在内核和用户空间中实现兼容性和最佳性能

图 3:Zynq UltraScale+ MPSoC 中处理系统和可编程逻辑组件用途的不同之处。(图片来源:iWave)

图 3:Zynq UltraScale+ MPSoC 中处理系统和可编程逻辑组件用途的不同之处。(图片来源:iWave)

AMD ERNIC IP 有效地将 RoCE v2 堆栈卸载到 FPGA 上,由 ERNIC 控制器管理不同模块之间的握手,以促进数据传输。 它生成工作队列条目,并向 ERNIC IP 发送通知(门铃)。 同时,Zynq UltraScale+ MPSoC 的 100G 以太网子系统管理 MAC 和物理层,而数据模式生成器则负责生成原始数据和视频数据模式。

精确时间协议 (PTP)

PTP (IEEE 1588 标准)时间戳在以太网网络系统间的时间同步过程中具有至关重要的作用。 这种同步对提高实时应用性能极为重要,可实现纳秒级的同步和低延迟数据交换。

设置要点

这种设置的显著特点包括:

- 利用 AMD ERNIC IP 通过 RoCE v2 实现 100G 以太网

- 可靠的连接传输类型

- 用于数据包处理的 RDMA SEND、RDMA READ 和 RDMA WRITE

- 支持 RDMA 即时发送和 RDMA 即时写入报文类型

- 使用 XRPING 和 PERFTEST 应用进行 RDMA 性能测试

- 用于 RAW 和视频数据模式的自定义数据模式生成器

- 在数据旁插入 PTP 时间戳

从 Zynq UltraScale+ MPSoC 开发套件到服务器 PC 的视频数据传输的详细吞吐量统计数据显示,Zynq UltraScale+ MPSoC 具有令人印象深刻的性能,能够以超过 100 fps 的速度处理 8K 视频,以超过 400 fps 的速度处理 4K 视频。

潜在应用

通过基于融合以太网的 RDMA 与 ERNIC IP 的集成,为众多行业开辟了新的途径,极大地增强了一系列应用的连接性、性能和效率,这些应用包括:

- 数据中心和云计算:促进云架构中的高效服务器通信并加速数据处理

- 视频/图像采集和传输:有助于多媒体应用、广播和虚拟现实 (VR) 环境

- 存储解决方案:加快存储设备和服务器之间的数据传输,从而提高存储系统的性能

- 高性能计算 (HPC):提高数据传输速度,减小高性能计算集群内的延迟,从而加快计算任务和模拟速度

- 物联网边缘设备:实现传感器和设备之间的实时数据收集和传输

随着对速度更快、效率更高的数据传输解决方案需求的持续上升,基于融合以太网的 RDMA 和 ERNIC IP 将在未来的高性能计算领域发挥举足轻重的作用。

结语

iWave FPGA 和 SoC FPGA 平台的广泛产品组合与其雄厚的技术专长相结合,使客户能够利用人工智能 (AI)、机器学习和边缘计算领域的最新进展来开发尖端产品。 通过与 iWave 合作,企业可以加快产品开发,降低风险,并在日益复杂的技术环境中保持竞争优势。

如需了解更多信息或探讨定制要求,请通过 mktg@iwave-global.com 联系我们。

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。