Verilog Ports - Part 7 of our Verilog Journey

2024-03-04 | By DWARAKAN RAMANATHAN

What are ports?

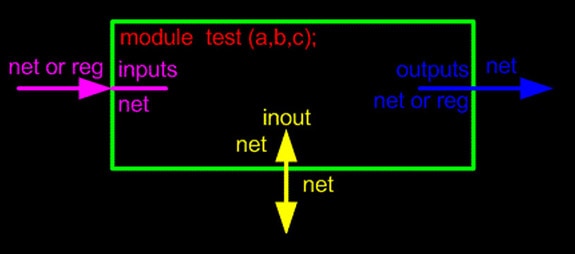

In Verilog and other hardware description languages (HDLs), a "port" is a fundamental concept that defines the interface of a module or an entity. Ports are used to specify how data and signals can enter or exit a module, making them crucial for communication between different parts of a digital circuit. Ports define the connections and interactions of a module with the external world.

There are three primary types of ports in Verilog:

- Input Ports (input): Input ports are used to bring data or signals into a module. They represent information that flows from external sources into the module for processing. For example, switches or sensors might be connected to input ports to provide data to a module.

- Output Ports (output): Output ports are used to send data or signals out of a module. They represent the results of processing or computations within the module. Output ports connect to components that need to receive the data produced by the module, such as LEDs or displays.

- Bidirectional Ports (inout): Bidirectional or inout ports allow data to flow both into and out of a module. They are typically used for communication between multiple modules or components, enabling data exchange in both directions. Bidirectional ports are versatile and often used in situations where data needs to be shared between multiple modules.

Here's a simple Verilog module with input, output, and bidirectional ports:

Copy Code

module ExampleModule (

input wire clk, // Input port (clock)

input wire reset, // Input port (reset)

output wire data_out, // Output port

inout wire bidir_port // Bidirectional port );

// Module logic goes here

endmodule

In this example:

- "clk" and "reset" are input ports that bring the clock and reset signals into the module.

- "data_out" is an output port that sends data out of the module.

- "bidir_port" is a bidirectional port allowing data to flow both into and out of the module.

Ports define the interface and connectivity of a module, enabling it to interact with other modules and components in a digital system. Properly defining and connecting ports is essential for creating well-structured and functional digital designs.

Unsigned and Signed Ports:

In Verilog, ports can be declared as either signed or unsigned, depending on the type of data they are intended to carry. This distinction is important for specifying how data is interpreted and manipulated within a module. Here's an explanation of signed and unsigned ports:

- Signed Ports:

- Signed ports are used when you want to represent and manipulate signed (both positive and negative) integer values.

- They are typically declared using the signed keyword.

- Signed ports are important when dealing with arithmetic operations that involve negative numbers, such as subtraction and multiplication/division that can result in signed values.

- When you use signed ports, Verilog ensures that the correct sign extension and arithmetic operations are applied.

Copy Code

module ExampleSigned (

input signed [7:0] input1,

input signed [7:0] input2,

output signed [7:0] result );

// Module logic goes here

endmodule

- Unsigned Ports:

- Unsigned ports are used when you want to represent and manipulate unsigned (non-negative) integer values.

- They are typically declared without the signed keyword.

- Unsigned ports are suitable for operations where negative values are not applicable, such as bitwise operations (AND, OR XOR) or when dealing with natural numbers.

Copy Code

module ExampleUnsigned (

input [7:0] input1,

input [7:0] input2,

output [7:0] result );

// Module logic goes here

endmodule

It's important to choose the appropriate type (signed or unsigned) based on the requirements of your design. Using the wrong type can lead to unexpected behavior and incorrect results in your Verilog modules. When working with signed data, make sure to use signed ports and apply appropriate arithmetic operations. When working with unsigned data, use unsigned ports to ensure that your module behaves as expected.

Conclusion:

In the world of digital hardware design, understanding Verilog ports is fundamental to creating efficient and effective circuits. From the early days of Verilog-95 to the rich capabilities of SystemVerilog, port declarations and usage have evolved to meet the demands of increasingly complex designs. Whether you're working with simple modules or intricate systems, knowing how to define, connect, and use ports is essential for success.

By mastering the nuances of Verilog ports, you gain the power to create modular, scalable, and maintainable designs. The ability to accurately specify inputs, outputs, and bidirectional connections ensures that your digital circuits behave as intended, whether you're designing for FPGAs, ASICs, or other digital platforms.

Have questions or comments? Continue the conversation on TechForum, DigiKey's online community and technical resource.