The Softer Option

投稿人:DigiKey 欧洲编辑

2015-03-11

Microcontrollers come in a dizzying array of shapes and sizes, but they all have one thing in common: their functionality is defined by the manufacturer. While their peripherals are designed to be as flexible as possible, often with the ability to modify certain parameters and some that even allow new features to be added through software — such as the PSoC family from Cypress Semiconductor, they still feature a fixed number of resources, allowing for relatively little customization. It is because of this fixed functionality that such a large number of variants exist.

FPGAs, on the other hand, are a comparatively blank canvas: their functionality is largely defined by the engineers using them with an almost limitless range of capacities to select. It is this freedom of design that enables teams to consolidate often many disparate digital (and increasingly analog) functions into a single, essentially tailored device that can better fit a particular design.

Variations on a theme

Programmable logic has evolved far beyond the PLD; traditionally popular for providing ‘glue logic’ in relatively simple designs. The availability of processor cores in the form of IP means OEMs can now choose to add a microcontroller (MCU) in often the smallest of FPGAs. While they may not offer total freedom of design, adding a soft core can deliver even greater design consolidation than simple combinatorial gates.

However, perhaps even more significantly, microcontrollers in the form of soft cores are normally optimized by the manufacturer for specific FPGA families, which commercially allows those manufacturers to offer the cores free, with no up-front cost or royalty. It means that if you’re using an FPGA and it has spare capacity, you essentially get an MCU for free. Furthermore, because the cores have been optimized to run in what is often a high-performance FPGA fabric, they invariably deliver greater performance than their discrete counterparts.

Not surprisingly — possibly because of its legacy, increased availability or just its size — one of the most prolific soft cores available is a version of the venerable 8051. Thanks to its longevity, the humble 8051 could be the most widely deployed instruction set architecture in the industry and despite coming under pressure from 32-bit alternatives (more of which later) it remains a firm favorite with developers, perhaps because of its relatively simple architecture and ease of use.

The market for general-purpose and ‘industry-standard’ soft cores targeting FPGAs is now so well established that Altera, Microsemi, Lattice and Xilinx all work with a third party provider to deliver a range of soft cores. The partner is Digital Core Design and it offers a range of 8-bit cores including versions of 8051, PIC16, HC11, as well as 32-bit cores based on the 68K CISC instruction set.

Customized solutions

Of course, part of the reason for using an FPGA is to create a customized design that delivers optimal performance for a given application, where a general-purpose 8-bit MCU may not quite be up to the challenge. In this case a more powerful 32-bit alternative may be required and, here, FPGA providers have opted to differentiate themselves by developing customized solutions.

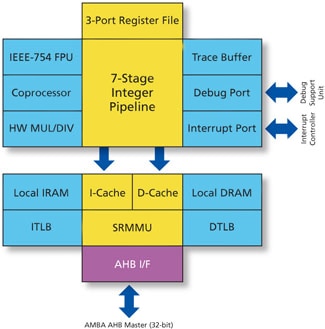

A good example is the LEON3 core, which is available both for Microsemi and Xilinx devices. It was developed by and is available from their mutual partner Aeroflex Gaisler AB. The core can be implemented in Microsemi’s Fusion, IGLOO, ProASIC3 and Axcelerator devices. It is also available for Xilinx’s Virtex-6, Virtex-5, Spartan-6, and Spartan-3 families. Based on the SPARC V8 instruction set with support for the V8e extensions, the core (Figure 1) is provided as synthesizable VHDL, which allows it to support extensive configurability, including cache number and size.

Figure 1: The LEON3 core offers 32-bit performance with a SPARC V8 instruction set.

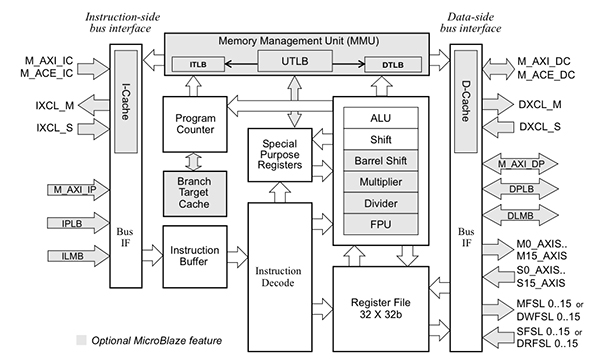

Xilinx also offers its own proprietary 32-bit embedded soft core in the form of MicroBlaze (Figure 2), which is supported by a wide number of its FPGAs and boasts over seventy user-configurable options.

Figure 2: The MicroBlaze soft core from Xilinx delivers 32-bit performance with extensive configurability.

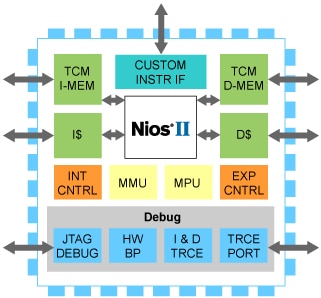

Configurability can be a key differentiator for developers and is, of course, the foundation on which FPGA vendors operate. It is not surprising that this extends to soft cores but, of course, supporting a core requires a compiler, which inevitably introduces some limitations on just how configurable a core can be. To overcome this, some vendors offer variants of their soft cores, like the Nios II from Altera (Figure 3), which it claims can be instantiated in any of its FPGAs. Nios II comes in three variants: Fast, Economy, and Standard, along with a range of free peripheral IP cores for features such as memory controllers and serial interfaces.

Figure 3: Altera offers three optimized variants of its Nios II soft core.

Industry standard

As well as a range of ‘legacy’ architectures including the 8051, optimized alternatives like LEON3 and customized solutions such as Nios II and MicroBlaze, FPGA vendors also have the option to support what has become probably the most ubiquitous instruction set architecture across the embedded electronics industry: ARM’s Cortex-M.

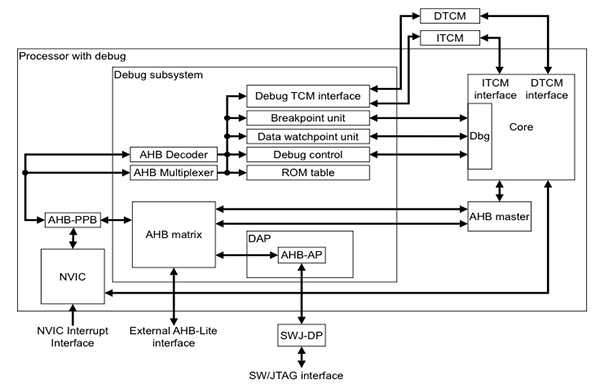

While not as instantly recognizable as the standard variants, the Cortex-M1 was developed by ARM specifically for implementation in an FPGA fabric. This low-gate-count version is based on the ARM v6-M Thumb instruction set architecture and also includes 32-bit Thumb-2 instructions. Extensions are available to support an operating system and debug (Figure 4). The core provides forward binary compatibility with the Cortex-M3, which means that software can be ported from the -M1 in an FPGA to an -M3 in an ASIC or standard part without recompilation.

Figure 4: The ARM Cortex-M1 has been developed specifically for embedding in an FPGA fabric.

Microsemi can support the Cortex-M1 in its Fusion, IGLOO and ProASIC3/E FPGAs, requiring between 600,000 and 1 million system gates (depending on the device), which equates to between 20% and 33% of the FPGA’s resources (if the debug features are omitted). Microsemi also offers a development kit, which integrates the Cortex-M1 in its ProASIC3/E device. Altera supports the Cortex-M1 in its Cyclone III family, where it consumes 2,600 Logic Elements.

Unlike simpler cores like the 8051, the Cortex-M1 requires peripheral cores to make it ‘work’, which could present a barrier to some developers. However, both Microsemi and Altera offer comprehensive tool suites that aim to make implementation as simple as possible; a reflection of how FPGA vendors are moving towards offering complete systems on chips as opposed to just logic devices.

Conclusion

The benefits offered by even the simplest of MCUs guarantees their continued use; however, with a mass migration towards low-cost 32-bit variants led by licensees of ARM’s Cortex-M family, it could be perceived that legacy devices are falling out of favor. In reality, FPGAs are not likely to replace standard MCUs, despite offering greater opportunity for integration, but it is feasible that the availability of soft cores for implementation in a range of FPGAs will sustain the popularity of some 8-bit families, for a new generation of developers to enjoy.

The support now available for soft cores, coupled with their low or even zero cost means they have already taken their place in the engineer’s toolbox, albeit a small place, today. As FPGAs develop further, they are likely to continue to integrate more hardwired functions, which include processor cores. However, it seems equally assured that the soft core will remain a viable option for many years to come.

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。