模拟基础知识 – 第 1 部分:SAR 模数转换器

投稿人:DigiKey 北美编辑

2020-04-15

编者按:模数转换器 (ADC) 将模拟世界连接到数字世界,因此是连接到现实世界的任何电子系统的基本部件。它们也是决定系统性能的关键因素。本系列文章探讨 ADC 的基础知识、各种 ADC 类型及其应用。本文为本系列关于模拟基础知识文章的第 1 部分,将讨论逐次逼近寄存器 (SAR) ADC。第 2 部分将讨论三角积分 (ΔƩ) 转换器。

现在仍然是一个模拟世界,因此要让感知的信息进入数字领域,需要进行某种转换。这一重任就由模数转换器 (ADC) 来完成。多年来,成功崛起的三种 ADC 拓扑结构是逐次逼近寄存器 (SAR)、三角积分 (S-D) 和流水线 ADC。这三种 ADC 拓扑结构截然不同,以便在不同的频率范围内工作,服务于从低频传感器应用到更高频率的 LiDAR 或卫星通信等所有领域。

SAR ADC 是第一种成为主流的转换器。随着时间的推移,这种转换器拓扑结构出现在各种应用中,包括过程控制、医疗和早期数字音频系统。这些应用受益于 SAR ADC 的 8 位至 20 位输出转换范围。但是,SAR ADC 赖以成名的原因是它会捕获模拟输入信号的快照,并使用多个信号快照来绘制一段时间内的图像。

本文将简要介绍与 SAR ADC 密切相关的信号链。接下来,通过分析负责 ADC 快照操作的基本输入级,深入研究该 ADC 拓扑结构。然后,本文将介绍 SAR ADC 示例解决方案——Analog Devices 的 AD7625BCPZ 和 AD4020BCPZ-RL7,着重讨论 ADC4020BCPZ-RL7 的内部模数转换机制。另外,还提供了合适数据采集系统的关键规格。

SAR ADC 的模拟信号链

SAR ADC 常用于自动测试设备、机器自动化、医疗设备和精密数据采集等系统中。在所有 SAR ADC 应用中,都存在一个需要适度 8 至 20 位分辨率数字表示的模拟信号,并且采样速率从接近 DC 到每秒 15 兆 (MSPS)(在撰写本文时)。

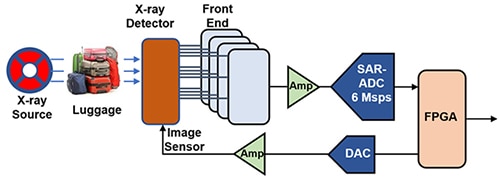

SAR ADC 能力强大,无需模拟前端 (AFE) 信号链即可工作。但是,如果设计人员的工作还包括在 SAR ADC 的前端成功呈现信号,则很有可能需要一定程度的信号调节(图 1)。

图 1:该示例 SAR ADC 信号链包括 X 射线探测器、AFE、放大器驱动器、Analog Device 的 AD7625BCPZ 6 MSPS 转换器,以及用于获得转换结果的数字接收器 (FPGA)。(图片来源:DigiKey)

图 1:该示例 SAR ADC 信号链包括 X 射线探测器、AFE、放大器驱动器、Analog Device 的 AD7625BCPZ 6 MSPS 转换器,以及用于获得转换结果的数字接收器 (FPGA)。(图片来源:DigiKey)

在图中,X 射线源经行李箱将信号发送到 x 射线探测器。X 射线设备的工作是在短时间内构建行李箱的完整图像,以减少旅客的不满。

前端获取探测器信号并执行信号调节功能,例如模拟增益和电平位移。然后信号被提供给 SAR ADC,在本例中为 Analog Devices 的 AD7625BCPZ。

SAR ADC 之前的放大器提供适当的稳定功能,在放大器与 SAR ADC 之间通常有一个一阶低通滤波器。该 SAR ADC 能够以高达 6 MSPS 的速度采样(每 167 纳秒 [ns] 采样一次),可以在短时间内获得多个快照。

SAR ADC 输入级的核心已简化

随着时间的推移,SAR ADC 经历了许多增强和改进,但在所有情况下,转换期间的主要活动都是电荷再分配,这是逐次逼近 ADC 最常见的实现形式之一。此外,与 S-D 和流水线转换器不同,SAR ADC 还具有零延迟优势。

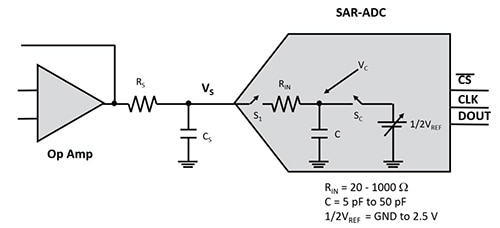

在最简单的层面上,很容易看到信号快照发生的位置。SAR ADC 输入核心包含输入信号采集开关 (S1)、电容阵列、转换开关 (SC) 和内部基准电压 (½ VREF)(图 2)。

图 2:驱动 SAR ADC 的运算放大器 (op amp),带有输出稳定滤波器。(图片来源:DigiKey)

图 2:驱动 SAR ADC 的运算放大器 (op amp),带有输出稳定滤波器。(图片来源:DigiKey)

SAR ADC 核心的工作方式如下:

- S1 打开,SC 关闭:断开输入级与模拟信号源的连接。

- C 上的电荷通过 ½ VREF 重新校准。这种重新校准使 SAR ADC 清零。

- 然后,S1 关闭,SC 打开:现在,该设备已连接到输入模拟信号。

- SAR ADC 在预定的采集时间内采集输入信号 VS。此采集时间可产生 S1 和 SC 开关噪声,以及放大器突然暴露于电容加载和开关噪声。

- 然后,S1 打开:这是发生信号快照的确切实例。

- SAR ADC 将 VC 处的信号转换为数字表示。执行此操作花费的时间就是“转换时间”。

SAR ADC 输入级的核心详细信息

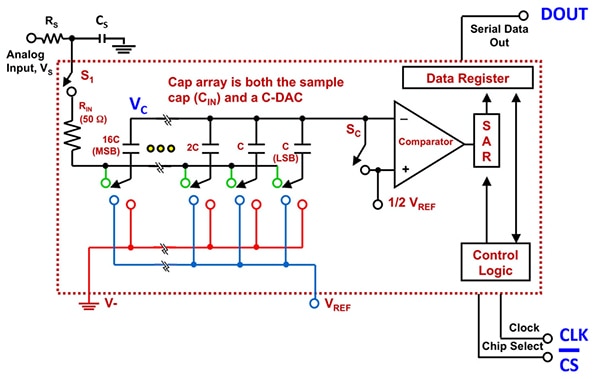

转换核心可对在 VC 处所采集信号进行电荷再分配。转换器电荷再分配的协调发生在核心中,由时钟进行门控。通过此过程,每个时钟控制的数字输出代码会到达 SAR ADC 的 DOUT 输出(图 3)。

图 3:4 位 SAR ADC 光幕具有完整的数字加权电容阵列:16C、8C、4C、2C 和两个 C。(图片来源:DigiKey)

图 3:4 位 SAR ADC 光幕具有完整的数字加权电容阵列:16C、8C、4C、2C 和两个 C。(图片来源:DigiKey)

在转换过程中,SAR ADC 算法首先会确定最高有效位 (MSB)。SAR ADC 通过在 V- 和 VREF 比较器输入之间切换 16C 电容器的底部,开始测试与 ½ VREF 相比的信号幅度。在 SAR ADC 转换线中,下一个比较是针对 ½ VREF 测试 8C(未显示),然后是 4C 测试,等等。

SAR ADC 输出转换详细信息

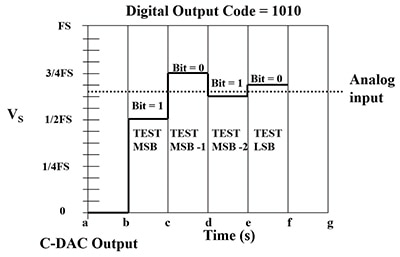

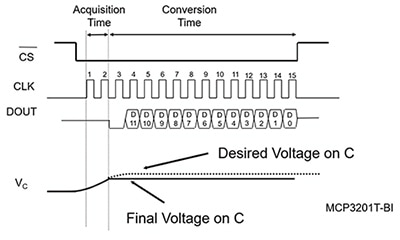

MSB 决策会立即通过 DOUT 引脚发送,而在进行 MSB 1 决策时,MSB 开关会保持冻结状态。SAR ADC 会一直执行此算法,直到最终选择最低有效位 (LSB)(图 4)。

图 4:4 位 SAR ADC 通过位决策对转换算法进行时钟控制,并通过 DOUT 引脚发送这些决策(如图 3 所示)。(图片来源:DigiKey)

图 4:4 位 SAR ADC 通过位决策对转换算法进行时钟控制,并通过 DOUT 引脚发送这些决策(如图 3 所示)。(图片来源:DigiKey)

在图 4 中,SAR ADC 时钟控制的位决策顺序是从 MSB 一直到 LSB。所有转换数据在时钟控制下继续通过图 3 右上角的 DOUT 立即输出。完整的吞吐时间通常需要足够的时间来采集信号,并且每个位需要一个时钟周期。

SAR ADC 转换挑战

设计人员必须了解信号的建立时间量,以确保从转换中捕获正确的模拟值(图 5)。

图 5:12 位 SAR DAC 的转换时序示意图。每次完整的转换需要 16 个时钟。(图片来源:DigiKey)

图 5:12 位 SAR DAC 的转换时序示意图。每次完整的转换需要 16 个时钟。(图片来源:DigiKey)

在图 5 中,输入信号 VC 在转换器输入开关打开之前未达到最终所需电压。出现这种情况是因为电路设计人员错误地计算了放大器输入信号的建立时间。

AD4020BCPZ-RL7 20 位 1.8 MSPS SAR ADC 通过延长采集相位的同时仍保持吞吐率,降低了信号采集的复杂性。它具有 100.5 dB 的低信噪比 (SNR)。

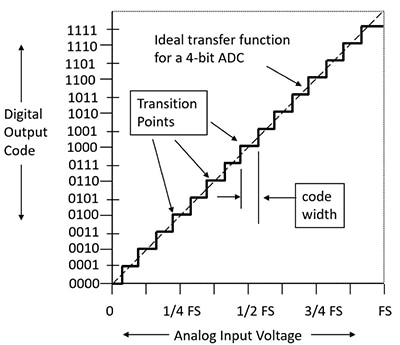

SAR AD 传递函数

ADC 的可能代码数等于 2N,其中 N 是位数。例如,4 位转换器具有 24 或 16 个单独的可用代码(图 6)。

图 6:理想 4 位 SAR AD 的传递函数或数字输出代码与模拟输入电压的关系图,应为一条直线。(图片来源:DigiKey)

图 6:理想 4 位 SAR AD 的传递函数或数字输出代码与模拟输入电压的关系图,应为一条直线。(图片来源:DigiKey)

绘制图像

SAR ADC 的吞吐率包括采集时间和转换时间,以让 Analog Devices 的 AD4020BCPZ-RL7 在 20 位分辨率下的吞吐率高达 1.8 MSPS。利用 AD4020BCPZ-RL7 吞吐速度,可以获取多个快照并创建用于机器自动化和医疗设备的数字图片渲染解决方案。

总结

从过程控制到医疗和消费类应用,SAR ADC 凭借获取信号快照的能力及不断提高的分辨率和速度,持续证明其价值。目前的 SAR ADC 具有 8 到 20 位的分辨率,吞吐率高达 15 MSPS。Analog Devices 的 AD4020BCPZ-RL 就是一个例子,其具有低噪声、高速、20 位、1.8 MSPS 的精度。但是,SAR ADC 转换器架构的发展还未结束。未来还会有更多产品。

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。