使用高效多核处理器打造更智能的语音产品

投稿人:DigiKey 北美编辑

2020-02-14

随着用户对 Amazon Alexa、Google Assistant、Apple Siri 和 Microsoft Cortana 等虚拟数字助理日渐熟悉并委以重任,对智能产品的需求几乎遍及所有应用领域。除了提供便利外,在工业系统和医疗保健应用中,虚拟助理在提高各种产品的安全性方面也发挥了日益重要的作用。然而,对于开发人员而言,这些产品的基础设计对处理器的需求有时相互冲突,既要增强性能,还需优化成本和资源占用并确保高效运行。

本文阐示了开发人员如何使用多核处理器(本文以 NXP 的 i.MX 8M Nano 为例)来满足众多应用对新兴智能产品处理和接口的各种不同要求,应用领域包括智能家居、工业自动化和医疗系统等。使用该处理器,开发人员可轻松实现具有高级音频处理功能的下一代语音型解决方案,本文着重介绍了具体应用方法。

智能产品的演化

语音助手技术的快速崛起,使用户期盼智能产品能实现更多功能。新兴产品既要响应语音命令,还需嵌入更多智能以处理来自传感器、相机和其他产品的各种输入数据。智能照明开关若只能打开和关闭灯或洗碗机以响应语音命令,还远远不够。随着应用的复杂化,其基础器件需要支持更多不同的传感器组合、3D 图形显示,并提高处理能力以使用人工智能 (AI) 方法。

大众希望产品更智能化,已然不只是出于对更高便利性的渴望。在工业自动化和医疗保健等关键应用领域中,设备能够主动提醒用户注意危险或病理状态就显得至关重要。工厂工人所戴的安全帽若能监测周围环境,他就能更快地避开危险;高危患者佩戴的微型医疗监护仪若能持续监测生命体征,医生就能在危机发生之前介入进行治疗。

上述及其他智能产品提出的特定设计要求虽与其目标应用一样各种各样,但大多要求产品具有高性能处理能力、多媒体功能和安全操作能力。对于开发人员而言,解决方案如需满足应用基本要求和这些功能需求,就必须提高性能以适应功能更强大的应用,同时缩小物理尺寸、缩减成本、降低功耗以满足用户期望。NXP 的 i.MX 8M Nano 应用处理器系列基于异构多核架构,可满足新兴智能产品设计的各种要求。

高性能内核

NXP 的 i.MX 8M Nano 是 i.MX 8M 处理器系列中最新的产品,旨在提供一个可扩展的多核处理平台。对于高端视频应用,NXP 的 MIMX8MQ5DVAJZAB 等 i.MX 8M 旗舰处理器提供的显示分辨率高达 4K,并可对 4K 高动态范围 (HDR) 视频进行硬件解码。对于 1080p 视频,NXP 的 MIMX8MM6CVTKZAA 等 i.MX 8M Mini 处理器支持 1080p 硬件解码。i.MX 8M 和 8M Mini 系列产品均整合了多达四个 Arm®Cortex®-A53 应用处理器内核和一个 Arm Cortex-M4F 微控制器内核。

相比之下,NXP 的 i.MX 8M Nano MIMX8MN6CVTIZAA 处理器整合了四个 Arm Cortex-A53 内核和一个 Arm Cortex-M7 内核。在 Arm Cortex-M 系列内核中(包括 Cortex-M4F),后者的性能表现最为出色。

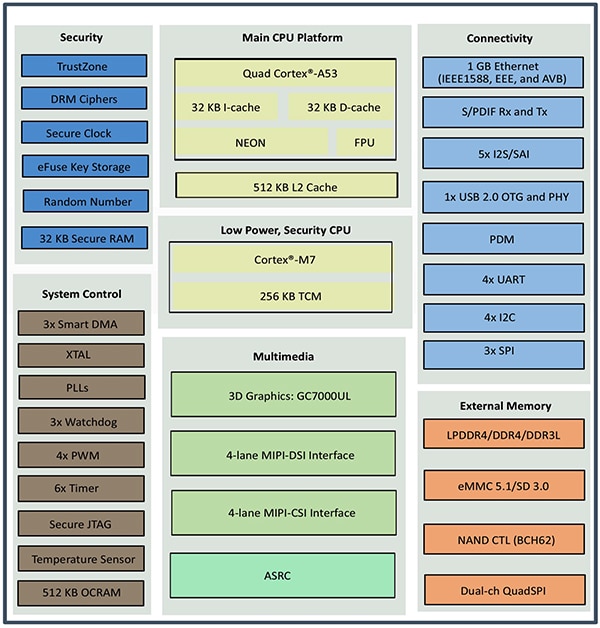

除了对处理器内核的优化外,i.MX 8M Nano 处理器还支持各种外部存储器件,并提供各种外部外设接口以满足消费类和工业应用的常见需求(图 1)。

图 1:NXP 的 i.MX 8M Nano 处理器整合了多达四个 Arm Cortex-A53 应用处理器和一个 Arm Cortex-M7 微控制器,具有专用硬件子系统、全面的外部外设接口,可满足消费类和工业应用的常见需求。(图片来源:NXP)

图 1:NXP 的 i.MX 8M Nano 处理器整合了多达四个 Arm Cortex-A53 应用处理器和一个 Arm Cortex-M7 微控制器,具有专用硬件子系统、全面的外部外设接口,可满足消费类和工业应用的常见需求。(图片来源:NXP)

i.MX 8M Nano 处理器系列具有多种不同的型号,使开发人员可轻松满足成本和性能方面的特定要求。例如,高性能产品集成了安全性、3D 图形显示、音频处理等各种专用子系统。另一些 i.MX 8M Nano 系列产品则可选择整合较少的 Cortex-A53 内核,更有图形功能较弱的 "Lite" 版本。

尽管如此,i.MX 8M Nano 处理器系列的所有产品均能提供新兴智能产品所需的应用性能和实时性能。

每个 Arm Cortex-A53 应用处理器内核都可提供高性能以执行应用软件,工作时钟频率高达 1.5 GHz,具有专用一级 (L1) 缓存——包括 32 KB 指令缓存 (I-cache) 和 32 KB 数据缓存 (D-cache),以及 512 KB 共享 L2 统一缓存。配合集成的浮点单元 (FPU),这些内核支持 Arm 的 Neon 技术——用于数字信号处理的高级单指令多数据 (SIMD) 操作,以及数据密集型应用的其他高级算法。

对于嵌入式系统要求,Arm Cortex-M7 微控制器内核的工作频率高达 750 MHz,可高性能执行要求低延迟和确定性操作的实时进程。为了进一步加快处理速度,该内核还具有集成的 FPU 和 256 KB 紧耦合存储器 (TCM),用于指令和数据缓存。

不过,对于复杂的实时处理任务,快速识别不同中断源的能力与原始处理能力同样重要。在 i.MX 8M Nano 处理器中,各个 Arm Cortex-A53 内核内置全局中断控制器 (GIC),Arm Cortex-M7 内核则具有嵌套向量中断控制器 (NVIC),可对近 128 个不同中断请求源发出的中断进行精细化处理,对应分类包括内核状态、定时器、外设接口事件、直接存储器访问 (DMA) 操作、专用硬件进程等。

异构多核处理

每个 i.MX 8M Nano 处理器内核都可独立提供强大的计算资源。实时性能和应用软件执行方面往往存在相互冲突的要求,致使智能产品设计难度陡增。然而,该处理器的多个内核配合使用,即可提供功能强大的计算平台,从而妥善处理这些要求。例如,基于该处理器的智能产品可使用 Cortex-M7 内核实时处理音频流,同时在一个或多个 Cortex-A53 内核上运行算法来分析结果数据,并为用户提供结果的 3D 图形显示。

然而,为了确保异构多核间协调处理的可靠性,多核系统需要仔细调度不同内核、专用硬件块和外设之间的处理操作和数据交换。在 i.MX 8M Nano 处理器中,这种调度是采用基于硬件的机制来实现的。在多处理环境中这种机制用于底层软件服务一般使用的信号量和消息发送。

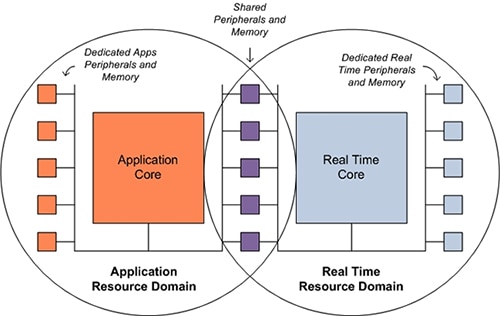

在嵌入式系统中,协调调度的对象则还需扩展至存储器和外设等硬件资源。为了执行此任务,该处理器集成了专用资源域控制器 (RDC),从而确保在适当时安全共享资源,或在需要时进行可靠隔离。因此,应用软件和实时代码可以各自控制其域内专用的资源,同时共享一组公共资源(图 2)。

图 2:NXP 的 i.MX 8M Nano 处理器采用基于硬件的机制,可确保 Cortex-A53 应用域或 Cortex-M7 实时域专用资源的隔离,同时在需要时实现安全的资源共享。(图片来源:NXP)

图 2:NXP 的 i.MX 8M Nano 处理器采用基于硬件的机制,可确保 Cortex-A53 应用域或 Cortex-M7 实时域专用资源的隔离,同时在需要时实现安全的资源共享。(图片来源:NXP)

针对智能产品的专用支持

只需使用 i.MX 8M Nano 处理器的多核和资源共享功能,开发人员即可实现语音助手和 3D 图形功能,构建复杂的新兴智能产品应用。凭借 i.MX 8M Nano 处理器内置的智能产品专用硬件支持,这些应用可进一步提高性能并减少软件占用空间。

在图形方面,处理器集成的图形处理单元 (GPU) 可提供 2D 和 3D 图形加速,支持 Vulkan、开放运算语言 (OpenCL) 和开放图形库 (OpenGL) 等标准图形库。集成的液晶显示接口 (LCDIF) 控制器支持 1080p60 显示(p 表示逐行扫描,帧率为 60 帧/秒)。

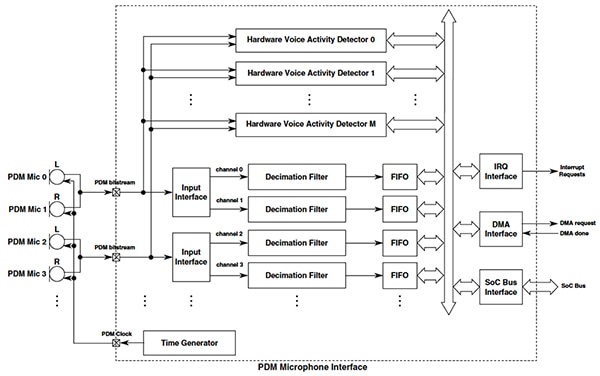

片上 GPU 可为内核分担显示处理,而另一组硬件子系统则分担了各种音频处理任务。通常情况下,这类任务会使基于常规处理器的系统速度减慢。针对麦克风输入处理,该处理器的脉冲密度调制 (PDM) 麦克风接口 (MICFIL) 可提供多级流水线,用 PDM 麦克风接收的 1 位输入生成经过滤波的 16 位脉冲代码调制 (PCM) 数据(图 3)。

图 3:NXP 的 i.MX 8M Nano 处理器具有 PDM 麦克风输入接口子系统,可为音频信号处理和语音活动检测提供独立的硬件流水线。(图片来源:NXP)

图 3:NXP 的 i.MX 8M Nano 处理器具有 PDM 麦克风输入接口子系统,可为音频信号处理和语音活动检测提供独立的硬件流水线。(图片来源:NXP)

在基于语音的典型应用中,设计人员只需在该处理器支持的八个 PDM 声道中选择其一,并连接 PDM 麦克风即可。在 PDM 麦克风接口子系统中,输入接口将来自一对麦克风的时分复用 PDM 数据进行组合,形成包含左右声道的混声道。

在每个声道的下一级,专用可编程抽取滤波器可提供不同的通带,具体取决于所需的输出速率和质量选择 (QSEL) 设置。具体质量设置选择包括高、中、低和另外三个较低的质量级别。例如,输出速率为 48 kHz 时,较低质量模式的滤波器通带设置为 10.5 Hz 至 11.25 kHz;相比之下,高、中、低质量模式的通带为 21 Hz 至 22.5 kHz。最后,各声道的滤波结果送入各自独立的先进先出 (FIFO) 缓冲区以生成中断,通过 DMA 传输或访问总线。

基于硬件的语音活动检测

PDM 麦克风接口提供一组硬件语音活动检测器 (HWVAD) 与音频信号调节流水线并行操作,用于监测所需的麦克风输入声道。(请注意:上图中,各 HWVAD 与混声道连接,但根据说明文档,与之相连的是各路声道,并且由寄存器 "VADCHSEL" 的名称可知,应为声道)。该处理器提供了各类设备寄存器以支持 HWVAD 操作,因而开发人员可按应用需求定义特定的 HWVAD 配置(表 1)。

|

表 1:NXP 的 i.MX 8M Nano 处理器寄存器常用于配置处理器 PDM 麦克风接口 (MICFIL) 中集成的硬件语音活动检测器。(表格来源:DigiKey,基于 NXP 提供的数据)

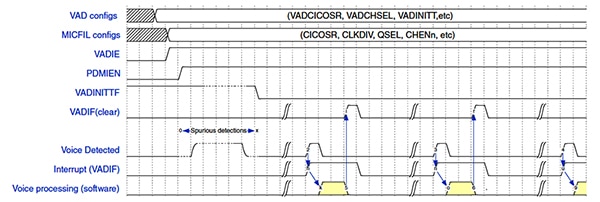

根据这些寄存器设置,HWVAD 使用内置的语音检测算法来识别语音活动。检测到语音活动后,HWVAD 随即生成中断以唤醒内核(通常是 Cortex-M7)以作进一步处理(图 4)。

图 4:根据开发人员编程好的设置,NXP 的 i.MX 8M Nano 处理器硬件语音活动检测器允许处理器内核休眠或执行其他处理,直至其检测到语音并需要进一步的语音处理为止。(图片来源:NXP)

图 4:根据开发人员编程好的设置,NXP 的 i.MX 8M Nano 处理器硬件语音活动检测器允许处理器内核休眠或执行其他处理,直至其检测到语音并需要进一步的语音处理为止。(图片来源:NXP)

在语音助手应用中,内核将检查音频流中是否存在相应的唤醒字。如果检测到唤醒字,则内核通常会将音频流交由应用支持的基于云的语音助手服务处理。

除了 PDM 麦克风接口子系统外,i.MX 8M Nano 处理器还具有五个同步音频接口 (SAI) 模块,支持 Inter-IC Sound (I2S)、audio codec 97 (AC97)、时分复用 (TDM) 音频、直接比特流数字 (DSD) 以及编解码器或数字信号处理 (DSP) 数据等多种标准音频格式。

开发人员常常需要将音频输入样本按需转换为其他采样率和分辨率,以满足特定应用要求。i.MX 8M Nano 处理器不是占用处理器周期来完成这类常见任务,而是使用集成的专用异步采样率转换器 (ASRC) 子系统。

ASRC 可同步处理多达 32 路音频声道,将声源样本自动转换为所需的采样率(介于 8 kHz 和 384 kHz 之间)和分辨率(每个样本 16、20、24 或 32 位 IEEE 单精度浮点数或定点数)。在此过程中,ASRC 将所有输入数据转换为 64 位 IEEE 浮点格式,确保根据需要对音频样本数据进行精确上/下变频,以获得所需的结果。

使用总电源控制器进行电源管理

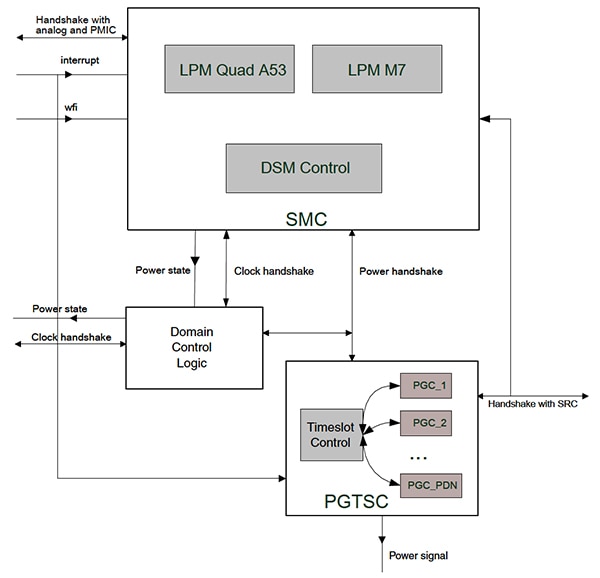

NXP 的 i.MX 8M Nano 处理器集成了多个处理器内核和硬件子系统,因此其架构中包含许多独立的电源域和电源模式,分别构建在各个内核和子系统中。为了管理这些内核和专用块的电源,i.MX 8M Nano 处理器包含一个精密的总电源控制器 (GPC),用于协调多个电源管理功能。在 GPC 中,系统模式控制器 (SMC) 用于管理各个内核的低功耗模式 (LPM) 和整体深度休眠模式 (DSM),而电源选通时隙控制器 (PGTSC) 用于管理时钟选通功能,通过禁用不活动子系统的电源来降低系统功耗(图 5)。

图 5:为了实现系统级电源优化,NXP 的 i.MX 8M Nano 集成了功能全面的电源控制器,用于管理处理器内核中内置的电源选通功能和低功耗模式。(图片来源:NXP)

图 5:为了实现系统级电源优化,NXP 的 i.MX 8M Nano 集成了功能全面的电源控制器,用于管理处理器内核中内置的电源选通功能和低功耗模式。(图片来源:NXP)

通过软件或硬件控制,GPC 可使用 PGTSC 中 20 个不同的时隙,使处理器中多个时钟选通电源域中的任一个上电或断电。此时,时隙控制器对时隙进行顺序操作,激活所有上电或断电请求后才会进入下一个时隙。除了满足特定的电源定序要求外,该方法还使开发人员能够减少系统上电或由低功耗或深度休眠模式唤醒时的电流激增。

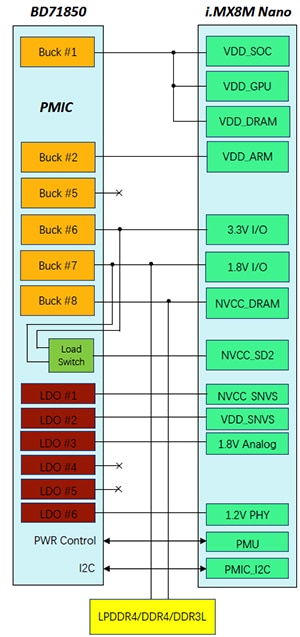

为 i.MX 8M Nano 处理器的多电源域供电十分简单。ROHM Semiconductor 的 BD71850MWV 电源管理集成电路 (PMIC) 专为支持 NXP 的 i.MX 8M Nano 处理器而设计,可提供处理器及其他系统外设所需的所有电源轨。实际上,BD71850MWV PMIC 本身集成了电源定序器,进一步简化了上电和断电的安全执行;供电对象不仅针对处理器,还包括外部存储器、传感器或系统中的其他器件(图 6)。对于开发人员而言,如需将 BD71850MWV PMIC 整合到设计中,除了常用去耦电容器(图中未显示)外,无需添加其他元器件。

图 6:NXP iMX 8M Nano 处理器的多个内核和硬件子系统需要多个电源轨,而 ROHM BD71850MWV 电源管理集成电路 (PMIC) 则提供了现成的解决方案。(图片来源:NXP)

图 6:NXP iMX 8M Nano 处理器的多个内核和硬件子系统需要多个电源轨,而 ROHM BD71850MWV 电源管理集成电路 (PMIC) 则提供了现成的解决方案。(图片来源:NXP)

开发支持

基于 i.MX 8M Nano 的设计中硬件接口要求相对简单,但是 NXP 甚至为开发人员免去了这项相对简单的设计任务,简化了处理器评估和新智能产品的原型开发。8MNANOD4-EVK 评估套件针对 i.MX 8M Nano 处理器提供了完整的开发套件和参考设计,其中包括 i.MX 8M Nano 处理器、BD71850MWV PMIC 和 Murata Electronics 的 LBEE5HY1MW Wi-Fi/蓝牙收发器模块,可作为即时评估和原型开发平台使用。除了多个接口选择和对应的连接器外,该评估套件还包括同步动态随机存储器 (SDRAM)、NOR 闪存和 NAND 闪存等一整套外部存储器。借助该评估套件,开发人员可以探索不同的工作模式和配置,包括从外部闪存启动,或使用已签名引导映像进行安全启动。

如果开发人员已准备好开始着手定制软件开发,NXP 为其提供了驱动程序、板级支持包 (BSP) 和中间件,可与该公司的 MCUXpresso 集成开发环境 (IDE) 和第三方 IDE 配合使用。如需构建利用机器学习方法的应用,开发人员可借助 NXP 的 eIQ 机器学习软件开发环境和 i.MX 优化推断库,例如支持 TensorFlow Lite 的 eIQ(适合基于 Cortex-M7 的推断),或面向 Arm 神经网络软件开发套件 (NN SDK) 的 NXP 端口(适合基于 Cortex-A53 的推断)。

总结

大众对语音助手产品的迅速接纳,也使其对下一代智能产品的期望值不断提升:这些产品既要提供出色的音频支持,还需提高性能、增强图形功能并确保高能效运行。然而,对于开发人员而言,这些产品的有效系统设计需要同时满足高性能应用软件执行和低延迟实时性能,但在相应的尺寸、成本和功率限制下,实现难度相当大。借助 NXP 的可扩展多核处理器系列,开发人员可轻松实现消费类、工业和医疗等众多应用领域对智能产品的设计要求。

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。

中国

中国