Understand the Power-Saving Options on Embedded Controllers to Improve System Power Efficiency

投稿人:Convergence Promotions LLC

2012-01-25

Embedded controllers of all sizes offer various operating modes to save power and/or conserve battery energy, both while the system is operating and when it is idling. However, the number of available modes has grown from just two or three to as many as a half dozen. Controller designers continue to shave operating power by allowing system designers to selectively turn off different portions of the microcontroller and adjust the clock rate in order to slow down the controller while it executes non-time-critical tasks.

Today, the industry employs microcontrollers in many types of systems for many different markets – consumer, medical, industrial, security, computer, and others. Many of these systems are battery powered, thus power consumption is a key specification to which designers must pay close attention. Even if the system is line operated, power consumption can also be a critical specification since many systems are in sealed enclosures, and the heat produced during operation must be kept to a minimum to prevent such systems from overheating. Energy efficient operation also makes it possible to eliminate fans or other schemes designed to remove heat.

Tricks of the trade

Since the early days of microcontrollers, chip designers most often implemented microcontrollers with static logic rather than dynamic logic so that simple clock gating could be used to stop all processor activity and reduce the power consumed by the controller to near zero (often just the leakage current). Static logic allows all the gates or memories to retain their state so that the functions can pick up where they left off when the clock is switched back on. However, dynamic logic requires that the logic elements continually get some activity, much like DRAMs get refreshed, in order to maintain their logic state. Unfortunately that means dynamic logic continually consumes some power even when the processor is idling.

As more and more functionality was integrated onto the microcontroller, clock gating became just one of many approaches to controlling power, since many sub-functions on the controller chip would often have to keep operating while the rest of the chip was idle; some of those functions include real-time clocks, interrupt inputs, counter/timers, and still other system support functions. In many cases, the controllers employ a second low-power clock oscillator that runs at 32 kHz to save power and provide timing for the real-time clock and other functions that must keep track of time, time intervals, or external events. In contrast, the processors in their active modes can run at clock speeds ranging from several megahertz to over one gigahertz.

Early attempts to reduce power consumption included reducing the operating voltage, reducing the clock speed, and clock gating. Such options gave the embedded controllers three basic operating modes – fully active, low-speed idle, and sleep. Reducing the operating voltage of the microcontroller has long been a traditional approach most chip designers have used to reduce power consumption. In part, the lower operating voltage was also driven by the reduction of the semiconductor process features. As transistor gate dimensions were scaled from several microns to fractions of a micron, operating voltages have dropped from 5 volts to 3.3 volts to 2.5 volts and now as low as 1.6 volts. A few companies have also demonstrated circuit operation at levels of less than one volt.

As the voltage goes down, so does the operating power consumption, but that is not all. Often the maximum clock speed has to be lowered, as the transistors lose some performance due to the lower voltages. Process tricks driven by high-performance microprocessor designs have greatly reduced those trade-offs, and today’s embedded processors deliver performance levels not thought possible a decade ago.

The latest generations of embedded controllers leverage many approaches to reducing power consumption – they can selectively control the clock rate, the functions that are active or idling at any point in time, and how the processor reacts to various external conditions. Designers have a choice of many highly-integrated microcontrollers that offer multiple operating and sleep modes which can reduce the multiple milliamps of operating power to a handful of nanoamps during deep sleep modes, and to just a microamp or two for operating modes between the deep sleep and fully-active modes.

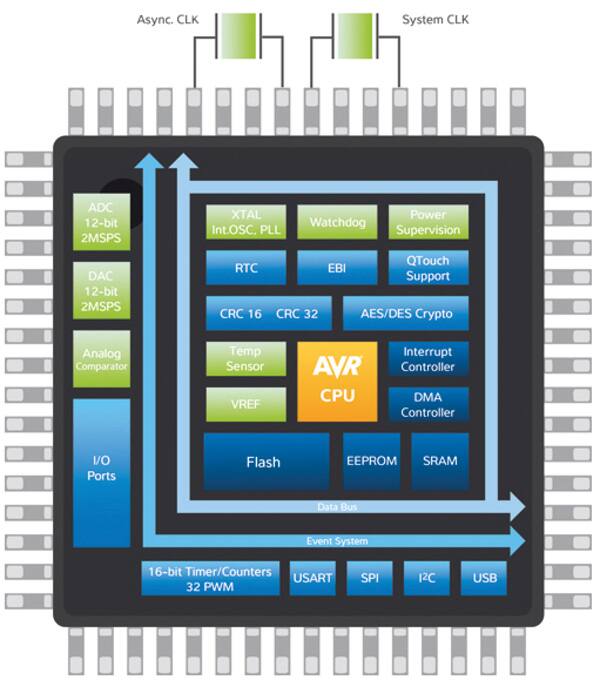

Atmel AVR XMEGA

To better understand the options available, let us examine some of the power-management options designed into several of the latest 8-, 16-, and 32-bit embedded processors. In the Atmel AVR® XMEGA® family of 8/16-bit microcontrollers (see Figure 1), the company included five software-selectable power-saving modes. A dedicated Sleep instruction is available to enter any of the Sleep modes. However before the chip can enter the selected mode, the programmer must configure the mode by selecting the appropriate resources that the mode will use:

- In the Idle mode, the CPU is stopped but the internal SRAM, event system, interrupt controller, and all peripherals continue their operation.

- A Power-Down mode saves the SRAM contents and register contents but stops the oscillators, disabling all the other functions until the next signal arrives on the two-wire interface port, or a pin-change interrupt or Reset occurs.

- A Power-Save mode allows the asynchronous real-time counter to run so that the application can maintain a timer base while the rest of the chip is sleeping.

- In Standby mode, the crystal oscillator/resonator oscillator continues its operation while the rest of the chip is sleeping. By allowing the oscillator to run, the chip achieves a very fast startup, eliminating the time needed to stabilize the oscillator (typically several thousand clock cycles).

- Lastly, the Extended Standby mode keeps the main oscillator and the asynchronous timer active. For even further power reductions, the peripheral clock to each on-chip peripheral block can optionally be stopped in the Active mode and in the Idle sleep mode.

Figure 1: Atmel AVR XMEGA MCU with sleep modes active (Courtesy Atmel).

The processor family can operate from supplies as low as 1.6 volts and consumes just 500 nA for the real-time clock with full SRAM data retention so that the chip can “wake up” very quickly.

There are about a dozen members in the AVR XMEGA family, and each has a different amount of memory and variations in other system resources, so we will just examine the ATXMEGA128D4 to see the differences in power consumption with various modes. When clocked at 32 MHz, the processor consumes about 11.4 mA, typical with a 3 volt supply. With a 2 MHz clock and a lower supply voltage of 1.8 volts, the same processor consumes just 510 µA. With a 32 kHz clock, current drops to just 30 µA with a 1.8 volt supply. When switched to its Idle mode, the processor draws just 2.8 µA at 1.8 volts and 32 kHz; 160 µA at 2 MHz; and 4.6 mA with a 32 MHz clock and a 3 volt supply. The full power-down mode with all functions disabled drops the current drain to just 100 nA.

Microchip PIC24FV32KA304

Keeping the power-saving modes simpler, designers at Microchip Technology Inc. only included two power-saving modes in its MIPS-based PIC32MX2xx/2xx family of microcontrollers – a Sleep mode and an Idle mode. Both modes halt the clock to the CPU in the controller. The Sleep mode has the lowest power consumption since it halts the CPU and most of the on-chip peripherals. Selected peripherals can continue to operate and can be used to wake the CPU from the Sleep mode. In the Idle mode, the CPU is again halted, but the system clock source is still available to the on-chip peripherals. Those peripherals can be individually directed to halt when the chip enters the Idle mode. Startup latency is also very short when exiting the Idle mode since the oscillator was active during Idle. The chips can operate from supplies ranging from 2.3 volts to 3.6 volts and at clock speeds from DC to 40 MHz. Dynamic current is typically about 0.5 mA/MHz, while the power-down current is about 44 µA and the Idle mode current is typically about 14.5 mA, both when powered by a 3.3 volt supply.

For its 16-bit PIC24FV32KA304 family of microcontrollers, designers at Microchip designed in five modes (not counting the Active mode) that help reduce current drain for various applications. In the Active mode, all functions are fully on and the chip can run at up to 32 MHz, drawing 12 mA from a 3.3 volt supply. In order to save power, designers can switch the chip to a Doze mode, an Idle mode, a Sleep mode, a Deep Sleep mode, or an “Off” mode. In the Doze mode, operating current can be reduced to just 8 µA, in Idle, the current drops to 2.2 µA; Deep Sleep drops the current to just 20 nA; and in the “Off” mode, just the device leakage current is present.

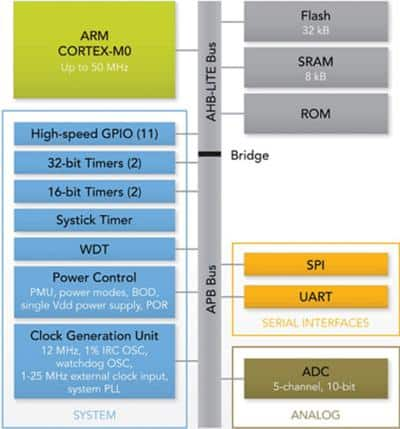

NXP LPC1102

Low-power 32-bit microcontrollers from NXP Semiconductors in the LPC1102 series (see Figure 2) keep the power reduction options simple as well. The controllers are based on the ARM® CortexTM-M0 processor core and they offer two reduced power modes – Sleep and Deep-Sleep. When in the Deep Sleep mode, an externally generated hardware signal is used to restart the processor, while in the Sleep mode the wake-up can be triggered by on-chip signals. In addition to the two power-reduction modes, the CPU clock rate can also be controlled by switching between clock sources, altering the set-up values for the phase-locked loop, and even by altering the CPU clock-divider ratio. These options allow the designer to trade-off power consumption versus performance based on the application requirements.

Figure 2: LPC1102 block diagram (Courtesy NXP).

Renesas SH7137

The proprietary SH family of 32-bit, reduced-instruction-set microcontrollers, part of the large array of microcontrollers offered by Renesas Electronics America, has as many as four different reduced-power modes. Specifically, the Renesas SH7137 offers a Sleep mode, a Software Standby mode, a Deep Software Standby mode, and a Module Standby mode. When active, the SH7137 draws about 80 mA when clocked at 80 MHz. The sleep mode keeps the clock running at 40 MHz and reduces the current drawn by the controller to 55 mA. The lower-power Software Standby mode further reduces the processor current to typically about 8 mA, while the Deep Software Standby mode reduces the current drain to a typical value of 2 µA. Lastly, the Module Standby mode allows designers to individually control the various on-chip peripheral support functions to selectively reduce power when the processor is active or in its sleep mode.

STMicroelectronics STM32F400

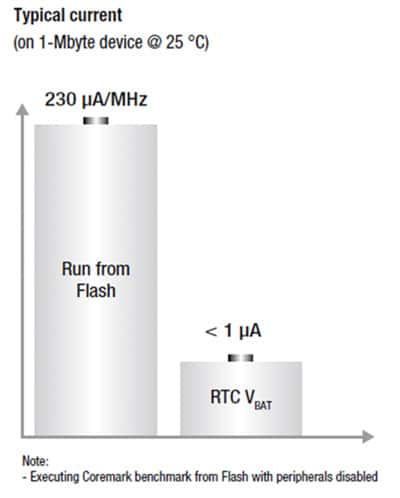

In its 32-bit ST32 family of microcontrollers based on the ARM Cortex-M3 and the Cortex-M4 processor cores, designers at STMicroelectronics have implemented three power savings modes. For instance, in the STM32F100xx value family of embedded controllers, designers can leverage the Sleep mode, the Stop mode, and the Standby mode to get the best compromise between low power consumption, short startup time, and available wake-up sources. The higher-performance series (see Figure 2) based on the Cortex-M4 processor core has additional power-saving resources – a separate battery power input for the real-time clock and a 4 kbyte back-up memory to store key contents from the main SRAM.

Figure 3: STM43 F4 power consumption (Courtesy STMicroelectronics).

Active processor power consumption depends on the operating frequency – the Cortex-M3-based processor draws 15.4 mA at 24 MHz and 6.7 mA at 8 MHz. With all peripherals disabled, the controller draws 10.3 mA at 24 MHz and 5.1 mA at 8 MHz. Sleep mode power is slightly lower, while in the Stop and Standby modes, typical current drain at a supply of 2.4 volts ranges from 1.7 to 23.5 µA. The more feature-rich Cortex-M4 controllers operate at frequencies of up to 168 MHz, and thus have a much higher current consumption. At 168 MHz the controller draws about 86.8 mA, while at 8 MHz current drops to 5.1 mA, which is comparable to the Cortex-M3-based processors at the same clock speed. With all peripherals disabled the current drain drops to 39.8 mA at 168 MHz and to only 3 mA at 8 MHz. In the Stop mode, the current stays below 1 mA, and in the Standby mode the current will be in the microamp range.

In the sleep mode, only the CPU is stopped. All the peripheral blocks continue to operate and can wake the CPU when an event or interrupt occurs (the timer reaches a set value, external interrupt signal comes in, etc.). In the Stop mode, additional peripheral blocks are turned off but the processor retains the contents of the on-chip SRAM and registers; all clocks in the chip’s 1.8 volt domain are stopped; the phase-locked loop and RC and crystal oscillators are disabled; and the on-chip voltage regulator can be switched from its normal mode to a low-power mode. A signal on any of the external interrupt lines will exit the processor from the Stop mode.

The lowest power drain can be achieved using the Standby mode, which switches off the on-chip 1.8 volt power domain and the oscillators. When the 1.8 volt power domain is switched off, the contents of the SRAM and registers are lost, so before going into this mode, critical data and register values should be saved to the registers in the Backup domain and standby circuits. To exit the Standby mode, either an external reset signal, a rising edge on the wakeup pin, or a real-time clock alarm can bring the processor back to its active mode.

Although there are many other companies offering microcontrollers with various power-saving features, these examples are typical of what other vendors typically offer. Of course there will be slight differences in the actual implementations, and that will require careful study of the data sheets and programming guides to ensure that you can minimize power consumption and make the appropriate performance/power trade-offs for your application.

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。