锁相环频率合成器的基本原理

投稿人:DigiKey 北美编辑

2021-02-03

高速串行通信总线的数据速率在不断提高,这就要求系统时钟具有更高的频率、卓越的稳定性、更高的频率分辨率和更高的信号纯度。直接数字合成器就拥有这些特性,但只限于在 2 或 3 千兆赫兹 (GHz) 以下的频率。对于高达几十千兆赫的频率,则需要一个解决方案。

这种解决方案首先采用基于锁相环 (PLL) 的模拟频率合成器,可产生高达 30 GHz 的时钟频率。然后,整数 N 分频合成器(将参考频率乘以整数值)和小数 N 分频合成器(将参考频率乘以非整数值)采用特殊技术,将相位噪声和类似的杂质信号降到最低。

本文以 Analog Devices 的器件为例,介绍整数和小数 N 频率合成器的设计。本文还强调了能使这些器件用于高速串行数据链路以及频率捷变雷达的创新技术。

整数 N 分频锁相环合成器

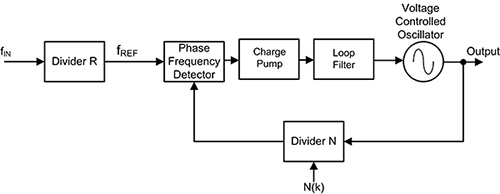

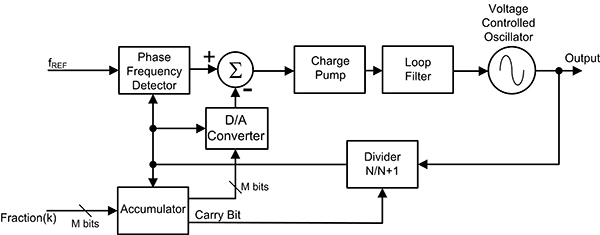

PLL 电路用于控制频率和相位。这些电路可以配置为时钟源、频率乘法器、解调器、跟踪发生器或时钟恢复电路。每一种应用都需要不同的特性,但所用的基本电路概念都相同。图 1 为配置为倍频器的基本 PLL 框图。

图 1:经典的整数 N 分频相锁环频率合成器的框图。(图片来源:DigiKey)

图 1:经典的整数 N 分频相锁环频率合成器的框图。(图片来源:DigiKey)

该电路的工作模式就是所有锁相环的典型工作模式。该电路基本上是一个能够控制压控振荡器 (VCO) 相位的反馈控制系统。输入信号被施加到预分频器上,然后预分频器将输入频率除以系数 R。预分频器的输出是参考频率,构成了相位频率检测器 (PFD) 的一个输入。

另一个 PFD 输入是来自 N 分频计数器输出的反馈信号。通常,如果 PLL 锁定,则两个信号的频率几乎相同。相位检测器的输出是一个与两个输入的相位差成比例的电压。如果环路就像启动时那样被解锁,或者如果输入频率有极大的瞬时变化,那么相位频率检测器就会工作,将 PLL 工作频率切换至所需的设置。当达到该频率时,PFD 返回至相位检测器模式,且其输出与参考频率和反馈信号之间的相位差成正比。

相位频率检测器驱动电荷泵,该充电泵是一个双极性开关电流源。这意味着它可以向 PLL 的环路滤波器输出正和负电流脉冲。

环路滤波器可以消除相位误差信号,同时也决定了 PLL 该的动态特性。滤波后的信号用于控制 VCO。注意,VCO 输出的频率是向相位频率检测器频率参考输入端提供的输入频率的 N 倍 ,是频率输入端的 N/R 倍。该输出信号通过 N 分频计数器返回至相位检测器。

通常,环路滤波器设计为与 PLL 应用所需的特性匹配。如果 PLL 要采集和跟踪信号,则环路滤波器的带宽将大于固定输入频率情况下的预期带宽。PLL 接受并锁定的频率范围称为捕获范围。一旦 PLL 锁定并跟踪信号,PLL 所遵循的频率范围称为跟踪范围。一般来说,跟踪范围大于捕获范围。PLL 环路滤波器还决定了信号频率能以多快的速度变化,同时仍保持锁定——例如,最高压摆率。环路滤波器带宽越窄,可实现的相位误差越小。其代价是响应速度变慢,捕获范围缩小。时钟应用中使用的 PLL 主要在固定频率下工作。一般来说,环路滤波器的带宽应远小于参考频率。

由于 PLL 输出频率是参考频率的整数倍,所以其频率分辨率与参考频率相同。要获得更精细的频率分辨率,就需要使用预分频计数器 R 来降低参考频率。

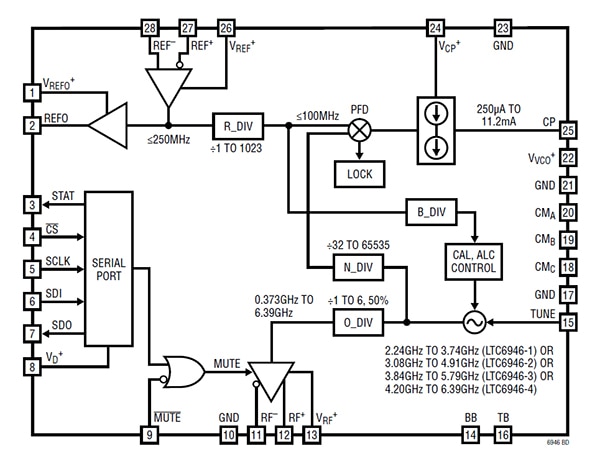

商用整数 N 频率合成器的例子如 Analog Devices 的 LTC6946IUFD-3#PBF 器件。这是一款 0.64 - 5.790 GHz 的低噪声频率合成器,集成了 VCO,具有出色的杂散性能(图 2)。该器件由四个合成器 IC 组成的系列产品中的一个,每个合成器 IC 都有不同的频率范围,频率总覆盖范围为 0.373 - 6.390 GHz。

图 2:带有集成 VCO 的 Analog Devices LTC6946IUFD-3#PBF 整数 N 分频合成器框图(点击放大)。(图片来源:Analog Devices)

图 2:带有集成 VCO 的 Analog Devices LTC6946IUFD-3#PBF 整数 N 分频合成器框图(点击放大)。(图片来源:Analog Devices)

该合成器需要一个由用户提供的外部环路滤波器,可以根据具体应用进行优化。内部有一个预分频计数器分频器,分频范围从 1 到 1023。环路分频器的范围为 32 到 65535。充电泵电流可在 250 微安 (mA) 至 11.2 毫安 (mA) 之间调节,以满足环路滤波器的要求。

小数 N 分频锁相环合成器

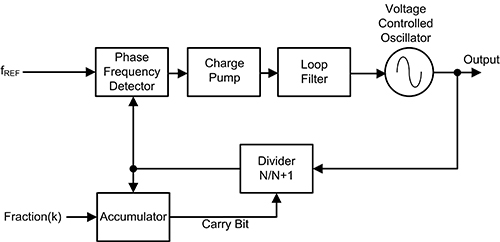

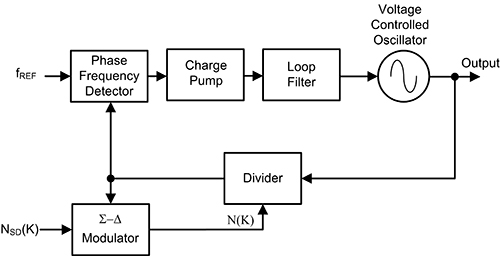

PLL 合成器的频率分辨率可以通过将步长值减小到小于整数值的方式来提高,即在环路分频器 (N) 中取小数为步长值。这是通过以动态形式改变或"抖动"倒计时值来实现的。这意味着分频器设置会在数量不变的 PLL 输出频率周期内保持 N 值不变,并周期性地以步进的方式将其改变为不同的值,如 N+1。例如,如果三个参考周期的分频设置为 4,第四个参考周期的分频设置为 5,那么有效倒计时值为 4.25。实现该目的的一种方法是使用累加器,如图 3 所示。

图3:使用累加器来调制分频器计数的小数 N 分频 PLL 合成器框图。(图片来源:DigiKey)

图3:使用累加器来调制分频器计数的小数 N 分频 PLL 合成器框图。(图片来源:DigiKey)

累加器对分频器的输出脉冲进行计数,每个 M(此处 M 为累加器模数)将输出会改变分压器输入的进位位。图 4 继续以把小数分频器设置值设置为 4.25 为例。

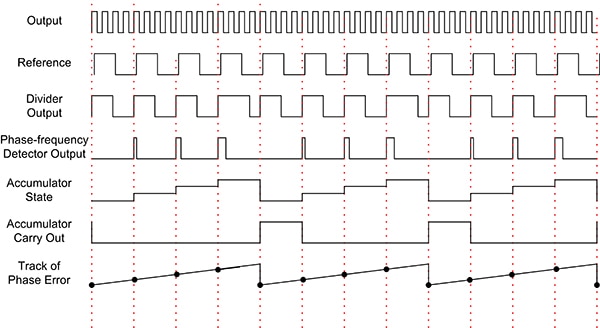

图 4:使用累加器的小数 N 分频合成器的时序图。(图片来源:DigiKey)

图 4:使用累加器的小数 N 分频合成器的时序图。(图片来源:DigiKey)

累加器由分频器输出驱动,并以 4 为模数,即 M 等于4。每隔第四个脉冲,累加器就会产生一个进位输出,将分频器计数递增 1。累加器复位并重新开始计数。分频器设置的增加会使输出频率发生偏移,从而产生累积相位偏移误差。相位误差的轨迹显示了脉冲值是时间的函数。

分频器的平均设置为 4.25,但合成器输出为相位调制,导致了输出中出现杂音。从累加器状态来看,很明显所跟踪的是相位误差。如图 5 所示,这可以用来消除调制。

图 5:利用经过 D/A 转换后的累加器状态来消除由于小数 N 分频抖动引起的相位调制。(图片来源:DigiKey)

图 5:利用经过 D/A 转换后的累加器状态来消除由于小数 N 分频抖动引起的相位调制。(图片来源:DigiKey)

累加器状态由数模 (D/A) 转换器转换为模拟值,并对相位频率检测器输出执行缩放和减法,以消除由于小数 N 分频抖动而产生的相位调制。进行该操作必须非常小心;如果校正信号不能精确匹配相位误差,输出端就会产生杂散音。

进入三角积分调制器

累加器的周期性特性是造成合成器杂散输出的原因。如果用三角积分调制器代替累加器,那么就可以使用数字技术来调制分频器计数,从而将杂散响应和噪声降至最少。这种替换如图 6 所示。

图 6:用三角积分调制器取代累加器,可以使用数字技术来改变分频器计数,以减少杂散响应。(图片来源:DigiKey)

图 6:用三角积分调制器取代累加器,可以使用数字技术来改变分频器计数,以减少杂散响应。(图片来源:DigiKey)

在三角积分调制拓扑中,实际上采用了两种常见数字技术。在第一种方法中,在较宽的数值范围内增大 N 分频计数的数量,使分频器系数的平均值会产生所需的小数分频值。这将减少基本的小数分频毛刺。基于累加器的合成器会在两个状态之间改变计数。这是一种一阶调制方法。n 阶三角积分小数分频 PLL 在 2n 个不同值之间调制 N 计数器。例如,三阶调制器将在 8 个不同的分频值之间交替,而四阶调制器则在 16 个不同的分频值之间交替。

第二种数字技术也称为抖动,涉及随机化 2N 顺序,使其成为伪随机。在仍然保持平均小数分频比的同时,将小数毛刺转化为成形随机噪声,这样就可以通过 PLL 进行滤波。

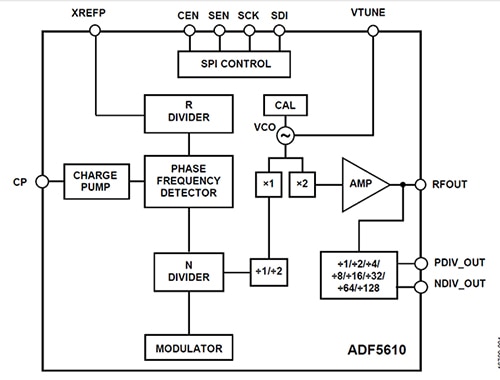

来自 Analog Devices 的 ADF5610BCCZ 器件就是一种三角积分小数 N 分频合成器的商业版本,这是一款集成了 VCO 的 0.57 兆赫 (MHz) 至 14.6GHz 低噪声小数 N 分频合成器(图 7)。

图 7:Analog Devices 的 ADF5610BCCZ 框图,该器件同时支持小数 N 分频或整数合成器配置。(图片来源:Analog Devices)

图 7:Analog Devices 的 ADF5610BCCZ 框图,该器件同时支持小数 N 分频或整数合成器配置。(图片来源:Analog Devices)

ADF5610 需要外接基准振荡器和环路滤波器。该器件包含一个集成 VCO,基频为 3650 MHz 至 7300 MHz。这些频率经过内部倍增后传送至 RFOUT 引脚。有一个差分输出,可以将倍增后的 VCO 频率以 1、2、4、8、16、32、64 或 128 的系数进行分频,这样可以产生低至 57 MHz 的射频输出频率。

ADF5610 采用先进的三角积分调制器,具有 24 位小数模数,可实现超低杂散水平。与所有使用三角积分调制器的合成器一样,该器件使用数字信号处理技术来求得所需的平均分频比。这个过程以 PFD 速率为时钟,产生被称为量化噪声的输出调制噪声,并具有高通频率响应。外部低通环路滤波器用于对这种量化噪声进行滤波,使其低于 VCO 相位噪声水平,从而防止噪声增加系统的整体相位噪声。

ADF5610 还包括一个精确频率模式,用于 0 赫兹 (Hz) 频率误差。在这种模式下,能够在相邻的整数 N 边界步长之间产生精确的频率,同时仍然使用完整的 24 位相位累加器模数。该器件实现了精确的频率步长,具有较高的相位检测器比较率,使得 PLL 在这种模式下能够保持优异的相位噪声和杂散性能。

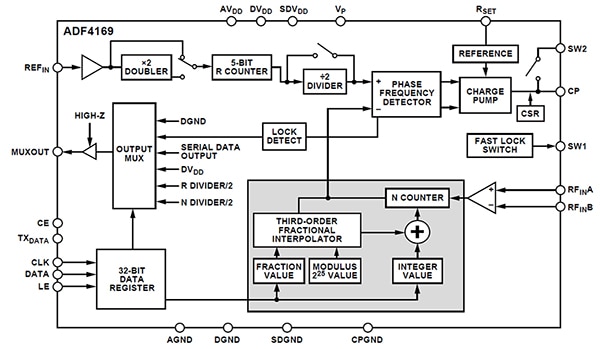

Analog Devices 的 ADF4169CCPZ-RL7 是另一款 PLL 合成器,可配置为整数 N 分频或小数 N 分频器件。其工作时的射频带宽高达 13.5 GHz,具有调制和波形生成功能。该器件使用外部参考频率输入、VCO 和环路滤波器。该器件包含一个可禁用的、用于小数 N 分频合成的三阶三角积分调制器,从而允许该器件在整数 N 分频模式下运行(图 8)。

图 8:Analog Devices 的 ADF4169CCPZ-RL7 采用三阶三角积分调制器。(图片来源:Analog Devices)

图 8:Analog Devices 的 ADF4169CCPZ-RL7 采用三阶三角积分调制器。(图片来源:Analog Devices)

ADF4158WCCPZ-RL7 频率合成器旨在用于对连续波 (FMCW) 雷达进行调频。该器件能够在频域内生成各种类型的调制波形,包括锯齿波和三角波。这是雷达应用必备的特殊功能。

总结

随着高速串行通信总线的数据速率不断提高,要求设计人员将目光投向其他领域,以获得系统时钟解决方案,而不仅仅是直接数字合成器,这种器件在 3 GHz 以下达到最佳工作状态。基于 PLL 的频率合成器采用整数 N 分频和小数 N 分频拓扑结构,为高频时钟、串行数据通信和雷达应用提供稳定的低噪声信号,其频率可达数十千兆赫兹。

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。