使用平移环模块快速构建低抖动、高频率的时钟

投稿人:DigiKey 北美编辑

2021-08-04

仪表和测量系统的设计者需要低抖动、无杂散的信号,以提供所需的信噪比 (SNR) 或误差矢量幅度 (EVM),以满足日益苛刻的客户要求。同时,他们也面临着减少电路板面积以及设计成本和复杂性的巨大压力。后者对于缩短开发时间以满足不断缩小的上市时间窗口至关重要。

为了应对众多的应用挑战,工程师们需要将他们的仪器和测量时钟解决方案从传统的定制分立设计过渡到更加集成的解决方案。实现这一目标的一个重要步骤是使用一个集成的平移锁相环 (PLL)。它允许传统的压控振荡器 (VCO) 信号进行频率上变频,同时充分保持固定的外部本地振荡器 (LO) 的抖动和相位噪声。

本文讨论了平移环在实现业界最低积分相位噪声方面的作用。通过举例,本文介绍了 Analog Devices 的 ADF4401A 平移环系统级封装 (TL SiP),并展示了它如何通过输出信号的亚十飞秒 (fs) 均方根宽带综合抖动能力和增强隔离度来满足性能要求,同时也满足了设计者的集成度、成本、复杂性和上市时间需求。

传统 PLL 与平移环操作

平移环的主要目的是产生一个锁定在输入参考信号上的输出信号,与传统的 PLL 相比,其带内相位噪声大大降低。

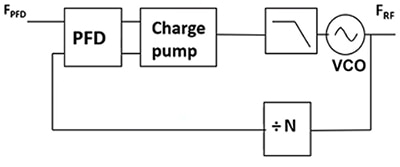

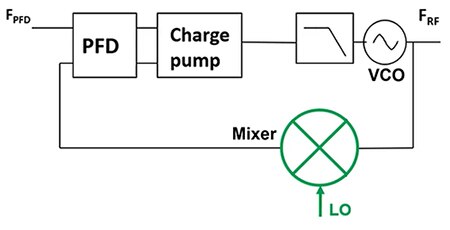

一个标准的 PLL 由一个反馈系统组成,包含一个相位频率检测器 (PFD)、充电泵、低通滤波器 (LPF) 、VCO 和一个反馈分频器 N(图 1)。

图 1:标准 PLL 锁定到一个较低频率 (FPFD) 参考,并产生一个输出频率 (FRF)。(图片来源:Bonnie Baker)

图 1:标准 PLL 锁定到一个较低频率 (FPFD) 参考,并产生一个输出频率 (FRF)。(图片来源:Bonnie Baker)

PFD 对输入参考信号的相位和反馈信号的相位进行比较,并产生一系列与它们之间的相位误差成比例的脉冲。充电泵接收 PFD 脉冲并将其转换为电流源或电流阱脉冲,进而调整 VCO 的频率,使其上升或下降。LPF 去除所有脉冲的高频能量,并将其转换为 VCO 可以使用的电压。VCO 的输出信号通过 N 分频器反馈给 PFD 块,完成这个环。

图 1 的频率传递函数是用公式 1 计算的。

![]() 等式 1

等式 1

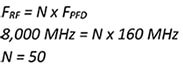

其中 FRF 是输出频率

N 是反馈分压器的比率(可以是整数或分数)。

FPFD 是 PFD 频率

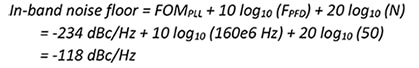

图 1 的带内噪声基底是用公式 2 计算的。

![]() 等式 2

等式 2

其中 FOMPLL 是 PLL 的带内相位噪声基底品质因数 (FOM)

考虑一个实例,带内相位噪声基底 FOM 为 -234 分贝/赫兹 (dB/Hz);PFD 频率 (FPFD) 为 160 兆赫兹 (MHz),输出频率 (FRF) 为 8 千兆赫兹 (GHz)。

对于这个系统,公式 1 用来计算 N 的值:

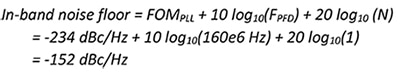

公式 2 用于计算带内噪声基底:

在上面的计算中,N 分频器对整个带内噪声基底的贡献很大,有 20log10 (50) ,相当于 34dB。N 值较小会降低带内噪声基底;但是,它也会降低输出频率。那么,我们如何产生一个高输出频率并保持较低的环路增益 (N)?

图 2:对于本例中的标准 PLL,与 N=1 的黄色下图相比,反馈分压器的噪声 (20log10 (N)) 比带内噪声高出 34dB。(图片来源:Bonnie Baker)

图 2:对于本例中的标准 PLL,与 N=1 的黄色下图相比,反馈分压器的噪声 (20log10 (N)) 比带内噪声高出 34dB。(图片来源:Bonnie Baker)

解决这个问题的办法是用一个下变频混合级取代 N 分频器(图 3)。

图 3:平移环使用混频器将 VCO 频率向下转换为 PFD 频率,而不是使用传统的反馈分频器。(图片来源:Bonnie Baker)

图 3:平移环使用混频器将 VCO 频率向下转换为 PFD 频率,而不是使用传统的反馈分频器。(图片来源:Bonnie Baker)

在图 3 中,混频器取代了反馈 N 分频器,导致回路增益等于 1 (N=1)。这种操作将大大减少反馈回路对带内噪声基底的影响。对于带内噪声的计算,N 的值现在等于 1。使用公式2,修改后的系统的带内噪声基底如下。:

新的带内噪声显示出 34dBc/Hz 的改善。

在图 3 中,混频器依赖于一个极低噪声 LO,称为偏移 LO。FLO ± FRF 必须等于 FPFD 以实现锁定。

在平移环结构中,偏移 LO 的相位噪声对于在射频输出端实现最佳性能非常重要。由于这个原因,工程师们通常会在压控表面声波 (SAW),或振荡器 (VCSO),或梳状发生器,或介质谐振器 (DRO) 的基础上设计一个偏移 LO。注意:如需获得偏移 LO 的设计支持,请联系 Analog Devices。

平移环的挑战

传统上,低噪声平移环的设计涉及众多电路块的实现,导致设计复杂,通常体积庞大,灵活性有限。此外,整个电路必须针对目标操作进行验证和特征化。例如,一个主要的设计关注点是对射频输出信号的 LO 泄漏(LO 与射频隔离)。这对工程师来说是一个需要解决的重大挑战。对于传统的设计,工程师们通常会进行多次设计迭代,以实现优化的性能和合适的隔离。

图 3 显示了 ADF4401A 是如何整合主要电路块以提供一个完全特征化的解决方案,并消除了传统上与平移环设计中的性能和隔离有关的困难领域。这种可编程的解决方案能够让工程师在第一次努力时就实现优化的性能,并加快上市速度。

评估 ADF4401A

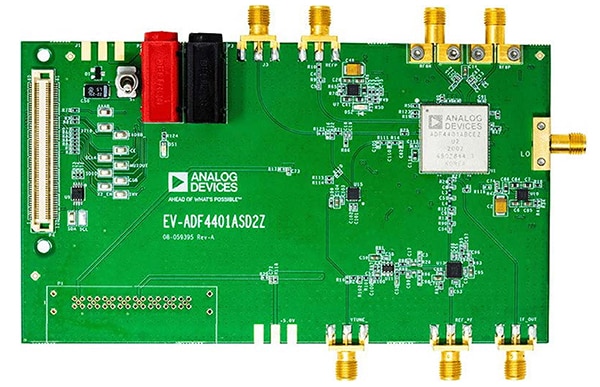

ADF4401A 旨在帮助工程师缩短高性能仪器上市所需的时间,使用的频率生成解决方案的射频带宽为 62.5 MHz 至 8 GHz。通过使用下变频混频器,ADF4401A 具有非常低的带内噪声,在 100 Hz 到 100 MHz 的宽带抖动约为 9 飞秒 (fs)。ADF4401A 内部的设计和布局技术使之典型无杂散动态范围达到 90 dBc。与传统的分立设计相比,18 x 18 x 2.018 毫米 (mm) 的封装尺寸大大减少了电路板空间。

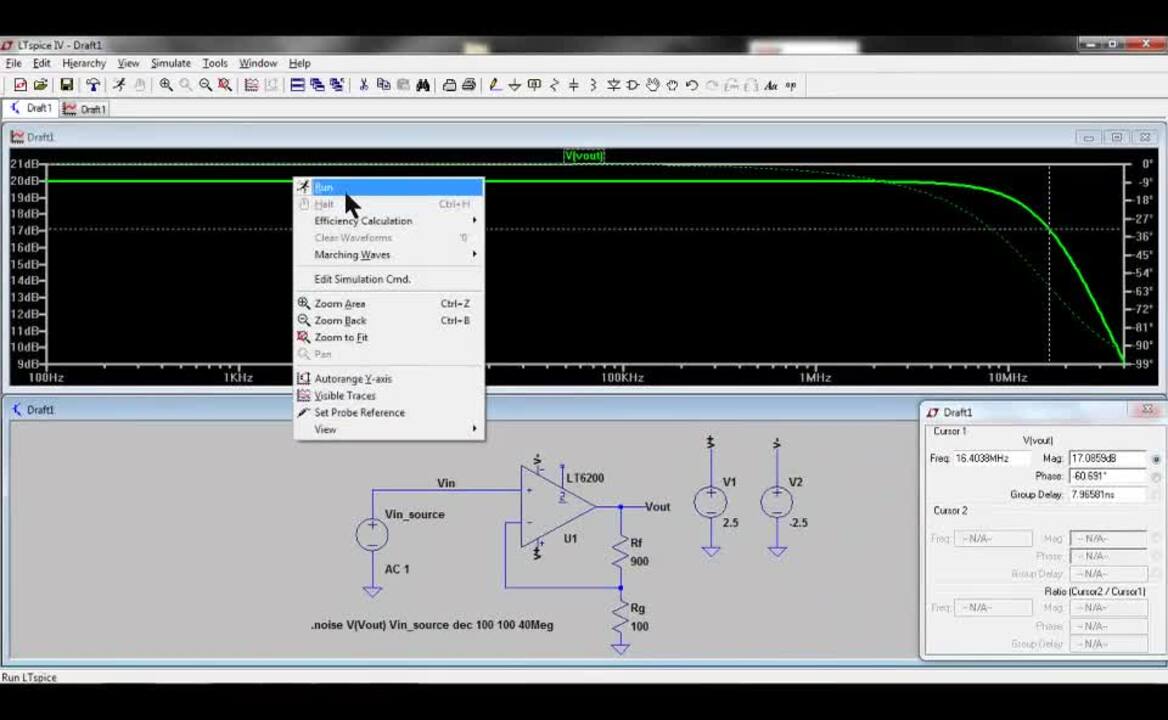

为了评估该器件的性能,设计人员可以使用 EV-ADF4401ASD2Z 评估板(图 4)。该板包括一个完整的平移环,包括一个外部 PFD (HMC3716)、一个有源滤波器 (LT6200) 和一个复用器 (ADG1609)。

图 4:用于 ADF4401A 平移环模块的 EV-ADF4401ASD2Z 评估板包括一个外部 PFD、一个 USB 接口和稳压器。(图片来源:Analog Devices)

图 4:用于 ADF4401A 平移环模块的 EV-ADF4401ASD2Z 评估板包括一个外部 PFD、一个 USB 接口和稳压器。(图片来源:Analog Devices)

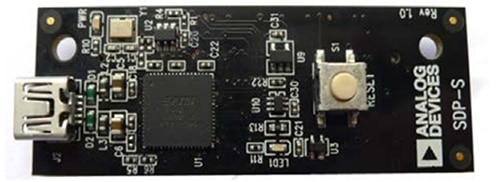

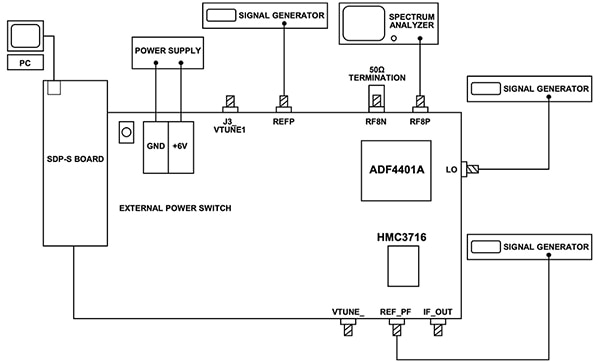

EV-ADF4401ASD2Z 包括带有集成 VCO 的 ADF4401A TL SiP、一个环路滤波器 (5MHz)、一个 PFD、一个 USB 接口和电压稳压器。此外,EV-ADF4401ASD2Z 需要 EVAL-SDP-CS1Z (SDP-S) 系统演示平台 (SDP)(串行)控制器板(图 5)。该板提供了一个从 PC 到 EV-ADF4401ASD2Z 的 USB 连接,因此可以对其进行编程。EV-ADF4401ASD2Z 套件中不提供该控制器板。

图 5:需要 EVAL-SDP-CS1Z(或 SDP-S)控制器板来提供从 EV-ADF4401ASD2Z 到 PC 的 USB 连接,以便进行编程。(图片来源:Analog Devices)

图 5:需要 EVAL-SDP-CS1Z(或 SDP-S)控制器板来提供从 EV-ADF4401ASD2Z 到 PC 的 USB 连接,以便进行编程。(图片来源:Analog Devices)

图 6 显示了 EV-ADF4401ASD2Z 系统的物理连接。相关分析 | 控制 | 评估 (ACE) 软件控制着 TL SiP 功能。电源来自外部的 6 伏电源。

图 6:EV-ADF4401ASD2Z 安装图显示了评估 ADF4401A 所需的设备和连接,包括 SDP-S 控制板、PC、电源、信号发生器和频谱分析仪。(图片来源:Analog Devices)

图 6:EV-ADF4401ASD2Z 安装图显示了评估 ADF4401A 所需的设备和连接,包括 SDP-S 控制板、PC、电源、信号发生器和频谱分析仪。(图片来源:Analog Devices)

建议与该评估板一起使用的设备包括一台 Windows PC、一台频谱分析仪或信号源分析仪,以及三个信号发生器。

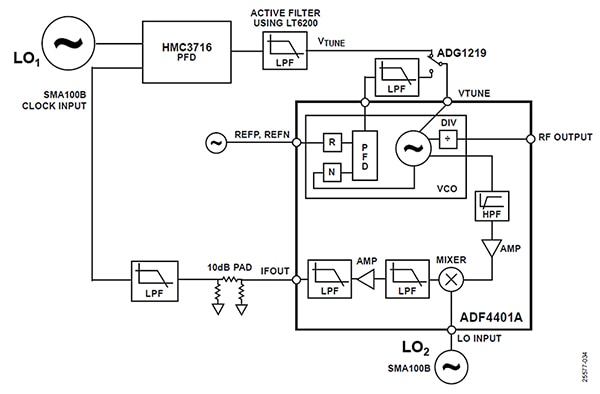

EV-ADF4401ASD2Z 的方框图显示了 ADF4401A 模块,以及 Analog Devices 的 HMC3716 PFD、LT6200 运算放大器和 ADG1219 SPDT 开关(图 7)。

图 7:EV-ADF4401ASD2Z 评估板框图显示了支持 AD4401A 平移环的关键部件。(图片来源:Analog Devices)

图 7:EV-ADF4401ASD2Z 评估板框图显示了支持 AD4401A 平移环的关键部件。(图片来源:Analog Devices)

使用能够在高频下工作的 PFD 是至关重要的,因为这可以最大限度地减少对分频器的需求,分频器会降低带内噪声响应。Analog Devices 的 HMC3716 的 1.3 GHz 相位比较频率能力使之非常适合用于 ADF4401A 的中频范围。这种电路能够同时比较频率和相位,因此不需要额外的电路来将频率引导到预定的输出频率。HMC3716 成为外部 PFD,完成偏移环。HMC3716 的高频工作范围和超低的相位噪声基底使其有可能设计出宽频带环路滤波器。

在图 7 中,具有 LPF 配置的 LT6200 运算放大器衰减了高频尖峰,而 ADG1219 开关完成了系统的平移环。

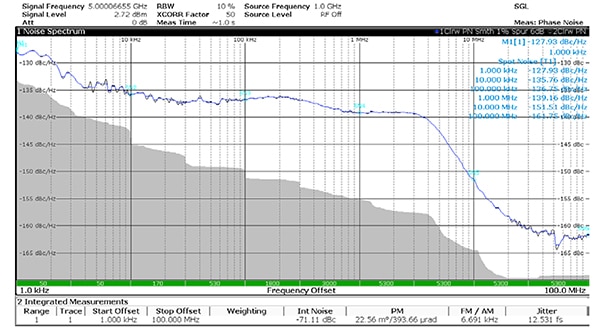

图 8 所示为 EV-ADF4401ASD2Z 评估板产生的带内噪声图和抖动测量。

图 8:5 GHz 输出的单边带相位噪声,外部 HMC3716 参考为 500MHz,外部 LO 为 4.5GHz。(图片来源:Analog Devices)

图 8:5 GHz 输出的单边带相位噪声,外部 HMC3716 参考为 500MHz,外部 LO 为 4.5GHz。(图片来源:Analog Devices)

在图 8 中,LO2 和 HMC3716 输入是一个 SMA100B 射频和微波信号发生器。该评估板的 LO2 带内噪声约为 -135 dBc/Hz,在最高 300kHz 的低偏移量下是很明显的。LO2、ADF4401A 模块、HMC3716 PFD 和环路滤波器带来的带内噪声约为 -140 dBc/Hz。内部相位噪声出现在 5MHz 和 50MHz 之间,该评估板的相位噪声基底大约为 -160dBc/Hz。这些因素加在一起,总计产生 12.53 fs 的 rms 抖动。

结语

高速仪器系统需要极低抖动的时钟,以确保输出数据不受影响。工程师们面临的挑战是,找到能够构建高速千兆赫时钟系统的合适设备。ADF4401A 平移环大大简化了构建时钟系统的器件选择,它提供了一个紧凑的模块,确保了在更高频率下的低抖动,同时也减少了电路板空间、成本和上市所需时间。

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。