New Components Call for a Hardware Comparison of Receiver Architectures

投稿人:DigiKey

2012-11-15

The battle between the superheterodyne radio architecture and the direct conversion radio architecture goes back to the 1930s. Each has its advantages for particular types of equipment. The simplicity of direct conversion hardware promises lower cost, lower power consumption, and less board space than with superheterodyne. Yet the hardware simplicity is offset by the software complexity to deal with inherent problems of DC offset. This article will probe the perceptions and realities of the hardware differences, while ignoring the software issues.

The tsunami of data transmitted over cellular networks was brought on by tremendous advances in smart phones, tablets, and other connected devices. This has increased the technical requirements, while pressuring suppliers to reduce costs. The circuitry required to support multiple channels in tiny base station form factors demands a variety of approaches to integration. With recent developments, just how significant is the difference between superheterodyne hardware and direct conversion hardware?

Review of the basic architectures

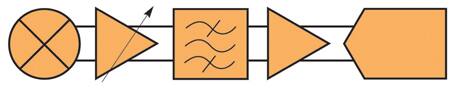

Edwin Armstrong invented the superheterodyne receiver architecture in 1918, according to most accounts. In this common type of receiver, the radio frequency (RF) signal is mixed with a local oscillator (LO) signal to generate an intermediate frequency (IF) which is then demodulated. The LO frequency is offset from the RF carrier frequency, creating images of the signal. The IF signal is passed, while all other images are rejected by filtering. The IF signal is converted to digital using an analog-to-digital converter (ADC) and then demodulated in the digital domain (see Figure 1).

Figure 1: Superheterodyne receiver architecture.

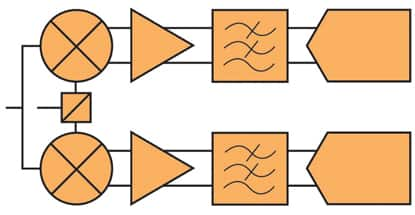

The direct-conversion receiver was developed a few years later as an alternative to the superheterodyne receiver. However, unlike the superheterodyne, the LO frequency is equal to the received signal's frequency. The single mixer is replaced by two mixers, one fed with the RF and LO signals, and the other fed with the RF signal and a quadrature LO signal. The result is a demodulated output which is digitized by two ADC converters at baseband (see Figure 2). In other words, the intermediate frequency is zero.

Figure 2: Direct conversion receiver architecture.

Evolution of hardware

The performance of the integrated circuit (IC) components continues to improve, while at the same time consuming less power and requiring less printed circuit board (PCB) area. The ADC resolution and sample rates have improved to allow wider bandwidth signals and higher input frequencies.

A major attraction of the direct conversion architecture is the lowpass filtering. The superheterodyne architecture requires a bandpass filter at the IF. In many cases, the bandpass filter is of a high order or a surface acoustic wave (SAW) type that requires a hermetic package and is often large and expensive. Lowpass filters are still considered to be small, simple, and low-cost, and therefore more attractive.

Latest hardware comparison

To attempt a comparison of cost, power, and board space, it is necessary to collect the components necessary to implement four receiver channels for a small base station suitable for 20 MHz signal bandwidth. Each superheterodyne receiver uses a single mixer, a variable-gain amplifier, a SAW filter, a second IF amplifier stage, and a high-speed ADC. Each direct conversion receiver uses an I/Q demodulator, two baseband amplifiers, and two high-speed ADCs. An example board layout is used to compare the estimated board space required for these components and the nominal power consumption is simply calculated from data sheet parameters.

Superheterodyne example

For four channels of superheterodyne, there are commonly available dual mixers in QFN packages of 5 mm x 5 mm – so two duals are required. With integrated balun transformers and internal matching components for the RF and LO inputs, the number of passive components is minimal – these will be ignored in this comparison since they are also required for direct conversion. Similarly, there are dual digital VGAs available in suitable frequency ranges available in 5 mm x 5 mm QFN packages. Again, two are required to implement four channels. A bit of filtering may be required following the mixer stages, so a few 0402 inductors and 0201 capacitors are in order. To achieve the required selectivity, a SAW bandpass filter is required for superheterodyne receivers. A separate SAW filter is required for each of the four channels. At RF frequencies, SAW filters can be quite small. In the common IF range from 70 MHz to 192 MHz, SAW filters can be found in 5 mm x 7 mm packages. Normally, another gain stage is required to make up for the insertion loss of the filter. However, a new quad ADC with integrated amplifiers is offered in a System in Package (SiP), the LTM9012-AB µModule® ADC from Linear Technology. At 15 mm x 11.25 mm, it is smaller than the equivalent quad ADC with four differential amplifiers and the associated bypass capacitors and anti-alias filter components. With 20 dB of gain, the LTM9012 achieves 68.5 dB signal to noise ratio (SNR) and 79 dB spurious-free dynamic range (SFDR).The amplifiers and the filtering within the LTM9012-AB limit the input frequency to about 90 MHz. Therefore, a 70 MHz IF is suitable.

The LTM9012 represents a different approach to integration. The µModule or SiP packaging allows separate die to be assembled along with various passive components on a laminate substrate, and molded such that it looks like a regular ball grid array (BGA) integrated circuit (IC). In this case, the ADC is optimized for low power and good AC performance. The amplifiers are traditional differential amplifiers, so the gain is set with resistors at 10 V/V or 20 dB. A true op-amp input simplifies the matching by isolating the high frequency sampling glitches from the signal path and also allows for single-ended signals to mate up with the differential ADC inputs internally. Equally beneficial is the anti-alias filtering that limits the wideband amplifier noise. In terms of overall board space, since all of the reference and supply bypass capacitors are inside the package, the overall system design can be packed very tightly without compromising performance. Such compromises often occur when reference and supply bypass capacitors are too far from or near digital signals which can then corrupt the data conversion process. Finally, the substrate allows the pin assignments to flow logically: analog inputs on one side, digital outputs on the other side of the package.

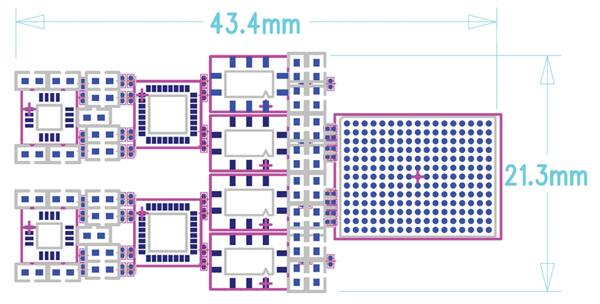

In this example, the number of active components is five, with four SAW filters and eighty other small passive components (see Figure 3). The overall area is about 43 mm x 21 mm = 903 mm², although not all of that area is utilized, so the effective area is more like 700 mm². For power calculations, this example uses the LTC5569 as the dual mixer, the AD8376 as the dual VGA and the LTM9012-AB as the combination of the second amplifier stages and quad ADC. The mixer is an active type, which operates over a wide 300 MHz to 4 GHz frequency range, so a single part can be configured to operate on any of the cellular bands from 700 MHz to 2.7 GHz. With best-in-class power consumption, it also has robust inputs that can withstand strong in-band blocking interference signals without significantly degrading its noise figure. The overall power consumption of the four channel system is 4.9 Watts, not including possible power dissipated in resistive dividers.

Figure 3: Example layout of superheterodyne receiver.

Direct conversion example

For four direct conversion channels our only options are individual I/Q demodulators, so four are required in 5 mm x 5 mm QFN packages. Some, like the LT5575, have integrated RF and LO baluns to minimize the number of external components. For the lowpass filter, multiple L-C and R-C sections are done. For the gain stage, the LTM9012-AB is again appropriate. As a quad, it only supports two direct conversion channels, so a second one is necessary.

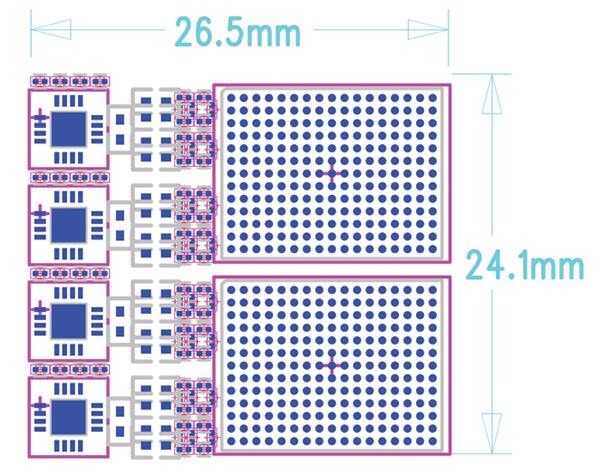

In this example, the number of active components is six, with eighty-four small passive components (see Figure 4). The overall area is about 27 mm x 24 mm = 648 mm². For power calculations, this example uses the LT5575 I/Q demodulator and two of the LTM9012-AB. The overall power consumption of the four channels is 5.1 Watts. However, the ADC is sampling at 125 Msps, which is common, but likely more than is necessary for 10 MHz. At 65 Msps, the same function could be done with much less power consumption in the ADC. Recalculating the power consumption brings the new total to 4.6 Watts.

Figure 4: Example layout of direct conversion receiver.

Perception and reality

Not too many years ago, a superheterodyne receiver used multiple mixers and multiple SAW filters per channel. SAW filters in the day could be 25 mm x 9 mm. The passive core mixers required additional gain stages to account for the insertion losses. Such recent history clouds the perception of the gap in hardware complexity between superheterodyne and direct conversion receivers. On a percentage basis, the board area used for the superheterodyne receiver is 39% more than the direct conversion, which is a significant percentage. In real PCB area, however, the difference is not so great. 39% of 903 mm² is 352 mm², or about the size of your thumb print. The power consumption difference is not significant on a percentage basis at all.

The reality is that integration continues, sometimes slowly and sometimes in great leaps. The recent examples that apply to the superheterodyne are products such as the LT5569 dual active mixer. The recent example of integration that applies to both architectures is the LTM9012 quad ADC with integrated amplifiers. However, the direct conversion architecture still requires twice the number of ADCs.

Conclusion

The direct conversion receiver architecture for cellular base stations is simpler than the superheterodyne receiver architecture, at least in terms of hardware. Recent products allow multichannel implementation of superheterodyne receivers to be much smaller than before. While still larger on a percentage basis, the difference may not be significant. Therefore, the superheterodyne is expected to remain the preferred receiver architecture for cellular base stations.

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。