如何通过自举法解决模拟高压输送难题

投稿人:DigiKey 北美编辑

2019-10-01

对于自动测试设备或精密控制系统而言,要提供它们经常所需的数百个模拟电压,无疑是一项独特的挑战。传统的运算放大器 (op amp) 无法提供这样高的输出电压摆幅,而分立放大器替代方案则需要高度调整,并会占用更多的 PC 板空间。

不过,还有另一种选择:自举高压轨至轨输出运算放大器和一对能够承受高击穿电压的 FET 的组合。

本文将介绍高模拟电压存在的问题以及解决这些问题的常用方法。然后展示如何使用来自 Analog Devices 的高压精密放大器,以及来自 Microchip Technology 和 Infineon Technologies 的高压 MOSFET 来应用自举法。

这些器件将用于创建一种精密、高性能的解决方案,以提供两倍于标称值的放大器信号范围,同时还能以极小的电路板空间提供更高的性能。

高模拟电压的设计选项

有些应用要求的输出电压摆幅高于典型的高压单片运算放大器可以产生的摆幅。使用分立晶体管的放大器设计是实现宽电压摆幅的方法之一。这种设计方法较为灵活,能够针对特定应用定制放大器。但是,分立晶体管设计会使用更多的零件,需要设计人员投入更多的时间和精力。此外,由于器件匹配和温度梯度的问题,在分立设计中也很难达到所需的精度。

分立高压放大器的替代方案是高压运算放大器模块。这些模块大幅简化了设计人员的工作。高压模块通常是兼顾高电压和高功率运行的混合模块。与分立设计相比,这些模块的优势在于它们具有出厂指定的性能。虽然这些规格减少了设计人员的特征化工作,但混合模块价格昂贵。大多数情况下,高压单片运算放大器便可满足设计的大部分性能要求。

但是,在无法满足的情况下,通过自举单片运算放大器的电源,将其扩展到规格范围以外,便可以将可用的运算放大器选项清单从几种解决方案增加至数百种。虽然自举策略需要投入更多的工作,但与高压模块相比,这种解决方案的成本要低得多。这主要是因为有各式各样具有足够的出厂指定性能的单片运算放大器可供选择。请注意,自举不会影响放大器的 DC 规格,例如电压偏移、输入电压摆幅和输出电压摆幅。

电源自举技术

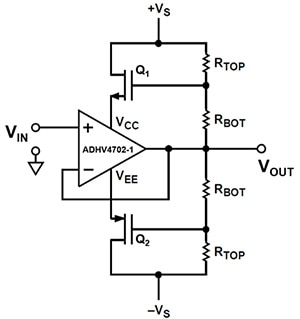

自举配置相对器件的输出电压来控制其电源电压。自举电路有一对分立晶体管和一个电阻型偏置网络(图 1)。

图 1:具有固定 +VS 和 -VS 系统供电电压的简化高压追随器自举原理图。VCC 和 VEE 器件供电电压随输出电压 VOUT 的变化而变化。(图片来源:Bonnie Baker,取自 Analog Devices 提供的材料)

图 1:具有固定 +VS 和 -VS 系统供电电压的简化高压追随器自举原理图。VCC 和 VEE 器件供电电压随输出电压 VOUT 的变化而变化。(图片来源:Bonnie Baker,取自 Analog Devices 提供的材料)

许多高压放大器消除了对自举电源的需求。例如,图中所示的 Analog Devices 10 兆赫兹 (MHz) ADHV4702-1BCPZ 是一款 ±110 伏电源,足以满足大多数高压应用的需求。但是,如果系统需要更高的电压,则自举法可轻松使该电路的工作范围加倍。

为了执行自举,Infineon Technologies 的 IRFP4868PBF N 沟道 MOSFET 可用作 Q1。该器件的击穿电压为 300 伏,ID 最大值为 70 A。Q2 是来自 Microchip Technology 的 TP2435N8-G P 沟道 MOSFET。其具有 350 伏的击穿电压。

在图 1 中,ADHV4702-1 精密放大器的工作供电电压范围为 ±12 伏至 ±110 伏。供电电压为 ±110 伏时,典型输出电压范围为 ±108.5 伏。±VS 等于 ±300 伏时,该自举电路是可实现 ±120 伏或更高输出摆幅的放大器的基础。

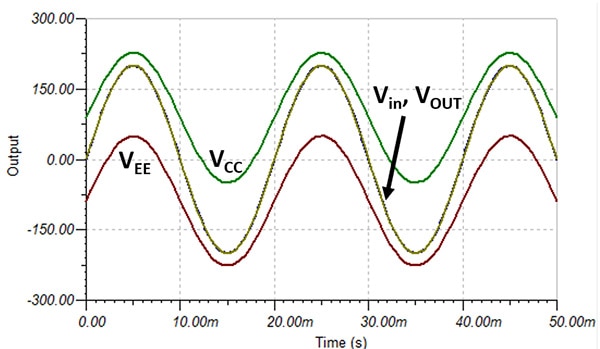

该自举概念也称为飞轨,它会连续调整放大器的供电电压,使其围绕放大器的输出电压 VOUT 保持对称。相应地,输出也保持在电源范围内。在追随器自举电路中,电阻分压器(RBOT 和 RTOP)将 VCC 与 VEE 之间的压差保持在恒定的 ±90 伏,而放大器的输出范围为 ±200 伏。Spice 仿真显示了这种浮动供电现象(图 2)。

图 2:Spice 仿真显示了浮动供电现象,其中放大器 Delta 电源(VCC 与 VEE 之间的压差)保持在大约 ±90 伏,而放大器的输出范围为 ±200 伏。(图片来源:Bonnie Baker)

图 2:Spice 仿真显示了浮动供电现象,其中放大器 Delta 电源(VCC 与 VEE 之间的压差)保持在大约 ±90 伏,而放大器的输出范围为 ±200 伏。(图片来源:Bonnie Baker)

在图 2 中,VOUT 等于 VIN,RTOP 等于 45 千欧 (kΩ),而 RBOT 等于 20 kΩ。RTOP 是最靠近外部电源(+VS 和 -VS)的电阻器,RBOT 是最靠近运算放大器输出 (VOUT) 的电阻器。请注意,在图 2 中,VCC 和 VEE 电压接近 +VS(300 伏)和 -VS(-300 伏)。当输出信号 (VOUT) 迫使 VCC 和 VEE 等于或超过 +VS 或 -VS 时,就会发生电路失真。

自举可提高任何运算放大器的信号能力。但是,放大器的压摆率会影响这种高压配置的动态性能。在图 1 中,运算放大器的压摆率限制了 VCC 和 VEE 响应动态信号的能力。自举放大器最适合电源缓慢变化的低频和 DC 应用。

自举设计实现

运算放大器电源的自举设计遵循三步过程:

- 评估放大器与 MOSFET 功率耗散之间的折衷

- 确定最大放大器输出摆幅并指定放大器供电电压

- 考虑电阻器的功率要求

在图 1 中,功率耗散在运算放大器与 MOSFET 漏源之间分配。放大器和 FET 的电压供应在规定的工作范围内。您可能希望用较低的电压为放大器供电,但这可能会给 MOSFET 造成压力。总功率耗散在放大器与 MOSFET 之间分配。

根据等式 1,最大运算放大器输出摆幅范围 (±VOUT-MAX) 与运算放大器电源(VEE、VCC)之间的关系决定了电阻分压网络。

![]() 等式 1a

等式 1a

如果运算放大器的标称供电电压等于 ±100 伏,并且最大输出摆幅范围等于 ±150 伏,则分压比等于:

![]() 等式 1b

等式 1b

此计算提供了一种简便的方法来确定该应用中的电阻值。但是,在选择电阻器时,请务必注意其中涉及到高电压,可能需要电阻器来耗散大量功率。请选择适当的电阻值,将散热量限制在相应的额定范围内。

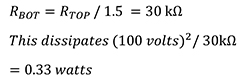

例如,RTOP 达到 150 伏,RBOT 达到 100 伏。使用 ½ 瓦额定电阻器时,功率耗散 (V2/R) 限制可使用等式 2 计算:

![]() 等式 2a

等式 2a

![]() 等式 2b

等式 2b

使用 45 kΩ 电阻器作为功率耗散限制因素时,RBOT 值将产生 2.5:1 分压器,其静态功率耗散限制的计算如下:

FET 选择

选择 MOSFET 的主要驱动因素是击穿电压。该电压必须耐受最坏情况下的偏置条件。当输出饱和时会出现击穿电压,这发生在一个 MOSFET 处于最大 VDS,而另一个 MOSFET 处于最小 VDS 时。例如,最高绝对 VDS 约为 300 伏,这是 VOUT-MAX(500 伏)减去放大器的总供电电压(VCC – VEE = 200 伏)得出的值。因此,MOSFET 的耐压能力不能低于 300 伏。此外,必须在 VDS 和工作电流均处于最坏情况时计算功率耗散。设计人员必须确保指定 MOSFET 在此功率水平下工作。

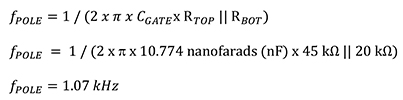

MOSFET 的栅极电容与偏置电阻器一起形成一个低通滤波器,击穿电压较高的 MOSFET 往往具有较高的栅极电容。在该电路中,偏置电阻往往介于几十 kΩ 至几百 kΩ 之间。使用这类高电阻值时,不需要多少栅极电容就能降低电路的速度。

根据公式 3,规格书中的 MOSFET 栅极电容值 (CGATE) 以及 RTOP 和 RBOT 的并联组合,决定了低通滤波器的极点频率:

公式 3

公式 3

注意事项

偏置网络的频率响应必须保持比输入和输出信号的速度快十倍。如果偏置网络降低电路速度,则放大器的输出可能会超出其电源范围。暂时偏离到放大器电源轨之外还有导致输入损坏的风险,而暂时饱和或压摆限制则有导致输出失真的风险。这些状况可能造成负反馈丢失、不可预测的瞬态行为,并可能因为反相而导致闩锁。

性能

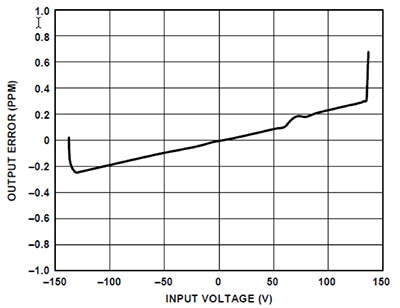

电源自举电路中的放大器可以进行配置,以获得更高的非反相增益。该自举运算放大器配置的工作方式与任何其他运算放大器增益级相同。您必须使用非反相配置。对于 DC 线性度测量,放大器的特性决定了结果(图 3)。放大器配置的增益为 20,电源范围为 ± 140 伏。

图 3:图中显示了增益误差与输入电压的关系,其中的增益为 20,电源电压为 ±140 伏。(图片来源:Analog Devices)

图 3:图中显示了增益误差与输入电压的关系,其中的增益为 20,电源电压为 ±140 伏。(图片来源:Analog Devices)

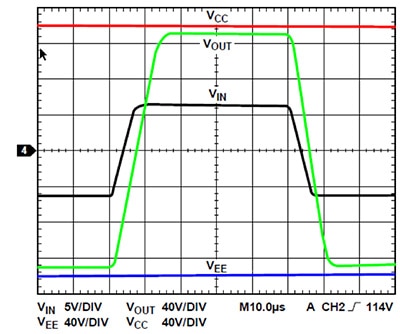

运算放大器的输出具有有限压摆率,其电源电压是其输出电压的函数。在运算放大器的输入端,步进调节可能会超出运算放大器的电源范围(图 4)。

图 4:增益为 20 且电源范围为 140 伏时的压摆率。在运算放大器的输入端,步进调节可能会超出运算放大器的电源范围,从而导致闩锁状态。通过在输入节点放置低通滤波器,可以避免这种情况。(图片来源:Analog Devices)

图 4:增益为 20 且电源范围为 140 伏时的压摆率。在运算放大器的输入端,步进调节可能会超出运算放大器的电源范围,从而导致闩锁状态。通过在输入节点放置低通滤波器,可以避免这种情况。(图片来源:Analog Devices)

在图 4 中,ADHV4702-1 的规定压摆率是 74 伏/微秒 (V/ms)。为了避免发生闩锁状态,设计人员需要在信号输入节点 (VIN) 使用低通滤波器。该压摆限制电路会将瞬态变化减小至小于或等于使用公式 4 计算的运算放大器压摆率:

![]() 公式 4

公式 4

其中 VSTEP 是信号源的最大步长,SR 是运算放大器的压摆率。

总结

要以低成本和极少的电路板空间驱动高模拟电压,一种绝佳的方法是自举高压轨至轨输出运算放大器与一对可耐受高击穿电压的晶体管的组合。Analog Devices 的 ADHV4702-1 高压精密放大器搭配 Infineon 和 Microchip 的高压 MOSFET,可用于创建这类精密的高性能解决方案,提供两倍于放大器标称值的信号范围,同时还能提供更高的性能。

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。