Designing Efficient Interleaved Power Factor Correction Solutions

投稿人:电子产品

2016-04-04

Power-factor correction (PFC) is essential for mitigating power quality problems as more sources of reactive loads tie into the grid. Among available PFC approaches, the interleaved PFC method enables engineers to build more compact PFC solutions using lower-cost components but requires highly complex control mechanisms, limiting its appeal to designers. Interleaved PFC solutions based on MCUs or specialized ICs integrate these control mechanisms, providing designers with a simplified approach for implementing efficient PFC capabilities in end products.

Defined as the ratio of the real power to apparent power, power factor represents the relative power available to run equipment. Reactive loads in equipment pull power factor well below 1. In fact, without correction, a typical switched-mode power supply has a power factor of around 0.6 with considerable odd-order harmonic distortion. When power factor falls below 1, voltage and current are out of phase, power spreads to harmonics outside of the fundamental frequency, and those harmonics travel down the neutral line to disrupt other power consumers.

Besides the need for utilities to generate more power to compensate for these inefficiencies, the harmonics create additional losses and dielectric stresses in capacitors and cables. Along with high noise emissions, the related increase in currents in motor and transformer windings lead to early failure of fuses and other safety components. By realigning the voltage and current waveforms so that they are in phase, PFC reduces harmonics required to comply with IEC 61000-3-2, which defines limits on harmonics emitted by electric equipment.

PFC methods

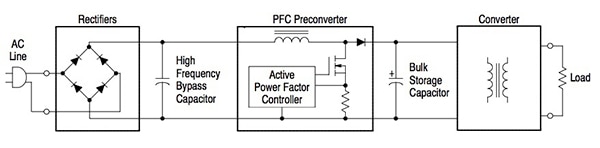

Although designers can implement PFC with passive components, active power correction allows use of smaller inductors and provides greater flexibility in dealing with different line voltages for products reaching international markets. Active PFC uses a switched-mode converter placed between the input rectifier and the output storage capacitor (Figure1). In this approach, a PFC control circuit shapes the input current to match the input-voltage waveform.

Figure 1: Placed between the input rectifier and output converter, a power-factor correction (PFC) circuit shapes input current to match input voltage. (Courtesy of ON Semiconductor)

The boost converter is typically the preferred converter topology for implementing PFC because this topology uses continuous input current. This input current can be manipulated with an average-current-mode control technique to force the input current to track the changes in line voltage. In addition, the boost-converter topology offers reduced current ripple and a simpler gate-driver implementation.

A typical single-phase boost PFC converter is a relatively simple design that combines a bridge rectifier, inductor, diode, switch, and output capacitor (Figure 2). In fact, the input bridge and additional components such as EMI filter generally already exist in most power converters. At the same time, the choice of these components is critical for ensuring efficient operation.

Figure 2: The boost-converter topology is preferred for PFC and simplifies manipulation of input current to track changes in input voltage. (Courtesy of Freescale Semiconductor)

More recent devices simplify component selection and matching by integrating most or all of the elements of a simple single-stage PFC converter on a single device – requiring very few additional components to implement PFC. In fact, members of the Power Integrations HiperPFS family such as the Power Integrations PFS7523 integrate not only a continuous-conduction mode (CCM) boost PFC controller and gate drive but also power components including an ultra-low reverse recovery diode and high-voltage power MOSFET. HiperPFS devices eliminate the need for external current sense resistors and the associated power loss, using a proprietary control technique that adjusts the switching frequency over output load, input-line voltage, and even input-line cycle.

Interleaved PFC design

The conventional single-stage PFC controller design nevertheless relies on a suitably large inductor and requires substantial filtering to reduce high-frequency ripple. An alternative topology replaces the single PFC boost converter with a two interleaved converters each operating 180° out of phase.

This interleaved approach significantly reduces the high-frequency ripple components of both the input current and the current into the output capacitor of the PFC pre-regulator. Compared to that of a single-phase PFC stage of equal power, the reduced ripple on the input current means designers can use smaller input capacitors and reduced EMI filtering. In addition, reduced high-frequency ripple current into the PFC output capacitor means designers can reduce its size and cost. Finally, the combination of reduced ripple and lower average current in each phase allows use of a smaller inductor size than in a conventional single-phase design.

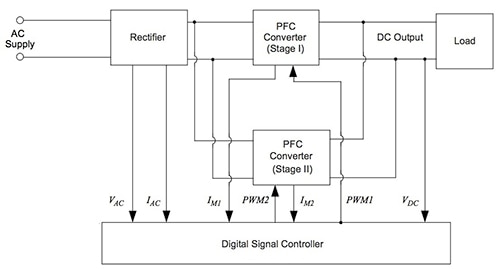

Designers can implement an interleaved PFC design with a highly integrated digital-signal controller (DSC) such as the Microchip Technology DSPIC33FJ06GS202 or Freescale Semiconductor MC56F8006. These DSCs combine a high-performance processor core with on-chip peripherals, including analog-to-digital converters (ADC), pulse-width modulators (PWM), and analog comparators. In this approach, the DSC uses its on-chip ADCs to monitor rectified input voltage and current, output voltage, and the MOSFET current for each stage (Figure 3). In turn, the device uses its integrated PWMs to control the switches in each converter while continuing to monitor the two converter switch currents to ensure equal sharing of the load between the two stages.

Figure 3: Digital-signal controllers combine analog peripherals needed to monitor input-voltage VAC and current IAC and output-DC-voltage VDC as well as drive each controller stage while measuring switch currents (IM1, IM2) to ensure equal load sharing. (Courtesy of Microchip Technology)

The primary disadvantage of this parallel converter approach is that the frequencies of the two converters are not identical, requiring methods to ensure their precise synchronization. In the past, this requirement has added the complexity of additional circuitry needed to implement appropriate monitoring and control. The use of integrated DSCs eliminates the need for additional control devices. Nevertheless, designers are still left with the task of implementing the sophisticated control algorithms required to ensure that the parallel converters operate precisely 180° out of phase (Figure 4).

Figure 4: Interleaved PFC depends on detailed measurement and control algorithms to ensure precise synchronization of parallel controllers. (Courtesy of Microchip Technology)

Integrated solutions

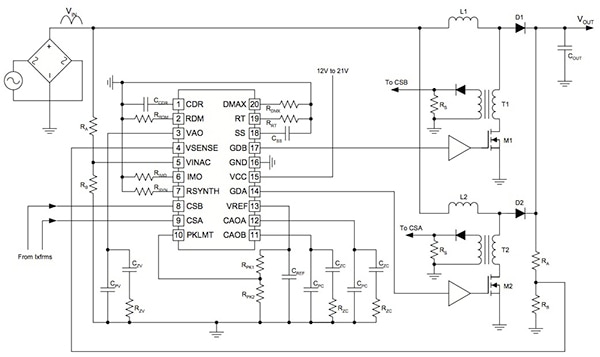

Specialized ICs offer an even simpler approach to interleaved PFC design, integrating complete control logic with the required peripheral functionality. Using these highly integrated devices, engineers can implement PFC with only the addition of the bridge rectifier and parallel boost converters (Figure 5).

Figure 5: Specialized ICs such as the Texas Instruments UCC28070 integrate comprehensive functionality required to interleave PFC with a minimum of addition components. (Courtesy of Texas Instruments)

For example, the Texas Instruments UCC28070 is designed to operate two parallel controllers 180° out of phase in a CCM PFC design. The device’s two independent current amplifiers ensure matched average current-mode control in both PWM outputs while maintaining a stable, low-distortion sinusoidal-input line current. Although an interleaved PFC typically incorporates only a pair of parallel converters, designers can combine multiple UCC28070s to provide an even number of additional phases for higher-power applications and to achieve even greater levels of input- and output-ripple current cancellation.

BCM solution

Although CCM PFC offers low peak-to-average current ratios for converter throughput power, it suffers a disadvantage in the impact of switching on the output diode. In CCM, forward current will normally be flowing through the diode when the MOSFET turns on. These high-voltage diodes are typically subject to extended reverse recovery due to slower recombination of minority carriers, which adds to the losses and ringing and ultimately to generation of high-frequency EMI harmonics.

In contrast, in critical-conduction mode (sometimes referred to as boundary-conduction mode [BCM] or transition mode), the inductor current is allowed to completely reach zero before the next switching cycle of the MOSFET is initiated. The zero-current switching of the boost diodes permits the use of less-expensive diodes without sacrificing efficiency. Furthermore, the input and output filters can be smaller due to ripple-current cancellation and effective doubling of the switching frequency.

Devices such as the Fairchild Semiconductor FAN9611MX, and Texas Instruments UCC28063 are integrated PFC controller ICs designed for implementation of interleaved BCM PFC. A key feature of these dedicated devices is on-chip zero-detect circuitry required for BCM operation: BCM designs operate at variable frequency, initiating a switching period whenever the current in the inductor reaches zero.

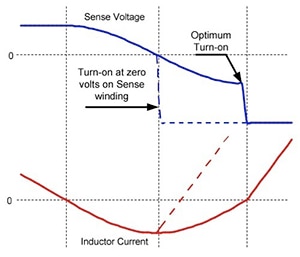

Typically, a zero-current detector monitors inductor current, using the voltage of the auxiliary windings on the inductor to indirectly sense when inductor current reaches zero. Although the simplest method of detecting a zero crossing uses a comparator threshold on the measured waveform, inductor current is actually at its maximum negative value when the voltage across the inductor is zero (Figure 6). If the MOSFET turns on at this time, all the energy stored in the parasitic capacitance would be shunted to ground, resulting in power loss. The Fairchild FAN9611MX’s internal sense circuit includes a differentiator able to sense a change in the slope of the sense voltage, allowing it to catch the valley of the sense waveforms and provide more efficient operation.

Figure 6: Advanced interleaved BCM PFC ICs such as the Fairchild Semiconductor FAN9611MX achieve higher efficiency by sensing the change in the slope of the sensed voltage rather than simply its zero crossing. (Courtesy of Fairchild Semiconductor)

Summary

Power-factor correction is critical for ensuring power quality – and maximizing the efficiency of power generation, transmission, and distribution. Interleaved PFC offers an efficient solution, reducing ripple and permitting use of smaller, lower-cost components. On the other hand, implementation of interleaved PFC designs requires more sophisticated control mechanisms that have limited its widespread adoption. Specialized ICs integrate the full complement of logic and circuitry required to control interleaved PFC converters, enabling engineers to implement advanced PFC designs more easily and effectively.

For more information about the parts discussed in this article, use the links provided to access product pages on the DigiKey website.

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。

中国

中国