Controlling the Human Interface

投稿人:DigiKey 欧洲编辑

2012-02-22

Microcontrollers are at the heart of the human-machine interface, translating sensor data into commands. Increasing performance from process technology and system architecture is allowing microcontrollers and FPGAs to handle more graphics and audio – either through hardware engines or software libraries – and provide a richer interface in the industrial environment.

The increasing integration and reducing cost of microcontrollers is driving the technology further into controlling the human interface in industrial designs. The ability to integrate LCD controllers and higher performance digital signal processing is allowing significantly more complex displays, including 3D graphics, to be implemented and displayed while keeping the cost and power consumption as low as possible. Adding other features such as touchscreen controllers and communications modules allows even more integration and makes the interface controller a key element within the system.

ARM has produced a new generation of processor cores, such as the Cortex-M3 and Cortex-M4, which have significantly higher levels of performance and DSP support and are allowing a new class of microcontrollers to handle a wide range of interface functions.

However, there are other ways to tackle the challenges. Existing cores can be supplemented with dedicated graphics hardware to make the most of existing software, while using field programmable gate arrays can provide either dedicated hardware or an optimized microcontroller, both combined with the technology to drive the displays.

Freescale Semiconductor’s Kinetis K40 is a microcontroller aimed directly at industrial human interface designs. It has a hardware touch-sensing interface, with up to 16 inputs, that avoids software polling method and a flexible, low-power LCD controller that supports up to 320 segments (40 x 8 or 44 x 4). The LCD blink mode enables low average power while remaining in low-power mode while a segment fail detection block guards against erroneous readouts and reduces LCD test costs.

The segment LCD controller supports up to 40 frontplanes and eight backplanes, or 44 frontplanes and four backplanes, all of which are configurable in software to avoid a costly re-design of the display equipment.

It uses an ARM Cortex-M4 core with DSP instructions delivering 1.25 Dhrystone MIPS per MHz running at 100 MHz, with up to 512 KB program flash memory. Additionally, there are 10 low-power modes to provide power optimization based on the requirements of the application. There is also a memory protection unit with multi-master protection as well as a 16-channel DMA controller that supports up to 64 request sources.

An interface needs to collect data from multiple sources. For this reason, there are two 16-bit SAR ADCs and a programmable gain amplifier (PGA) (up to x64) integrated into each ADC, as well as a 12-bit DAC and three analog comparators (CMP) containing a 6-bit DAC and programmable reference input.

To communicate with other parts of the system, the device includes a USB full-/low-speed On-the-Go controller through an on-chip transceiver as well as two Controller Area Network (CAN) modules, three SPI modules, two I2C modules, five UART modules and an I2S module. This means the device can act as the hub not just for the interface but also for other parts of the system.

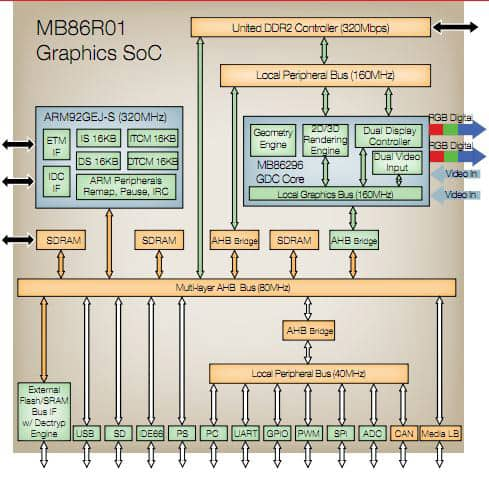

Fujitsu’s Graphics Display Controllers (GDCs) use an SoC architecture based on the ARM926 core. The MB86R01 incorporates Fujitsu’s well-established MB86296 3D graphics core and is built in Fujitsu’s standard 90 nm process to provide the optimal balance of power (low leakage current) and performance.

The MB86R01 Graphics SoC features a hierarchical bus system that isolates high performance functions, such as 3D graphics processing, from routine operations such as low speed I/O. Additionally, the ARM processor is designed to run at twice the rate of the graphics core to reduce memory bus contention between these two primary functions.

Figure 1: The MB86R01 graphics SoC from Fujitsu.

Central to MB86R01’s architecture is a full 3D geometry processing unit that is capable of performing all primary 3D operations including transformations, rotations, back face culling, view plane clipping, and hidden surface management.

This device features a display controller that supports two capture sources (YUV/ITU656 or RGB) and enables both upscaling and downscaling of the video image. The video may also be mapped to any one of the six display layers and may be texture-mapped to polygons to create special effects.

The display controller is also capable of dual digital outputs, supporting multiple monitor configurations in different resolutions. The content may either be the same or unique to each panel. The MB86R01’s six display layers may be viewed as six individual frame buffers or individual canvases that may each contain unique content. The layers can be optimally sized to save memory and improve system throughput and graphics performance. Consider a menu bar example. If the actual graphics area is only 60 x 400 pixels, the device allows the layer to be set to match the display area of 60 x 400 while underlying layers may be a full resolution of up to 1080 x 768. Once the layers have been created by either rendering or block transfers, the GDC blends the content in real time, eliminating the need for a final frame buffer which would impact performance and increase the amount of memory required.

In addition to multiple layers, the Fujitsu GDCs offer a variety of alpha blending and transparency options that designers can use to create special effects and to improve the anti-aliasing of bitmaps and fonts to make the interface easier to use.

The device also includes a wide variety of interfaces, from SD Card and IDE to USB, SPI, UARTS, and a Flash/ SRAM port. ADC and DAC are also included for capturing data.

There are other ways to use a microcontroller to build the human interface. Altera’s DK-DSP-3C120N Cyclone III development kit allows the designer to integrate the 32-bit NIOS processor core with a graphics engine and LCD controller block, both of which are exactly tuned to the requirements of the application. The low cost Cyclone III family of FPGAs allows the exact requirements of the design to be implemented in a cost efficient way.

The NIOS II processor can be configured with additional instructions specifically written to enhance graphics applications by using Altera’s Quartus design tool to generate a compiler to allow a developer’s C code to be compiled for that particular implementation. This can provide faster performance and more responsiveness for an industrial interface at the same time as reducing the size of the code and the memory requirements, reducing the cost of the equipment.

Figure 2: The Altera DSP Cyclone III development kit.

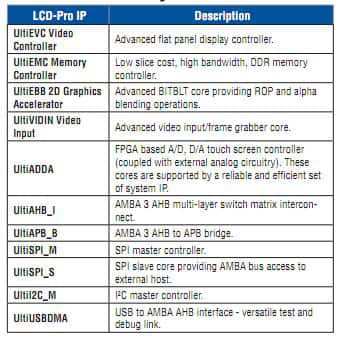

The LFE2-50E LCD-Pro graphics evaluation kit from Lattice Semiconductor enables the evaluation of a set of flexible, configurable IP cores for versatile and powerful display control, graphics, and video applications via a seven-inch TFT screen. The library is based around the industry standard AMBA bus architecture, allowing interconnection of the LCD-Pro IP with a wide range of system components compatible with the AMBA bus such as ARM processors.

Figure 3: The Lattice LCD-Pro graphics evaluation kit.

The LCD-Pro IP cores are targeted to Lattice FPGAs, specially optimized for the LatticeECP2 low-cost FPGA family. The library contains several IP cores with the ability to control a wide range of flat panel displays ranging from low-end CIF and QVGA up to high definition TFT, in 8, 16 or 24-bit color and tested in the field with more than 30 commercially available displays. The IP supports multi-layer image compositing available in display controller, supporting simple overlaying, color keyed transparency, alpha blending and alpha masking as well as variable layer color depth, size, positioning and smooth scrolling.

Figure 4: The Lattice LCD-Pro IP cores.

The kit can be used for building video modules handling a wide range of formats combined with graphics to build clear and usable human interfaces in industrial applications. All of this provides a powerful array of techniques for developing the very latest industrial interfaces. From dedicated hardware to software-configurable devices, these devices enhance the ability of the designer to control the display and provide the best possible human interface.

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。

中国

中国