为物联网设计添加高性能语音关键字检测:第 1 部分 - 使用 FPGA

投稿人:DigiKey 北美编辑

2018-09-27

随着“Alexa”、“Hey Siri”或“Hi Google”等多个产品成功响应关键词,关键字检测 (KWS) 已成为越来越多嵌入式应用的一项重要要求。虽然典型的先进 KWS 解决方案依赖于复杂的卷积神经网络 (CNN) 和其他深度神经网络 (DNN) 机器学习算法,但资源受限型产品的开发人员可以使用二值神经网络 (BNN) 获得所需的准确结果。

本文介绍了将 KWS 添加到可穿戴设备和其他低功耗物联网设备的优势,以及所面临的各项挑战。在描述 BNN 架构及其为何适用于资源受限型 KWS 应用之后,本文还介绍了一种通过低功耗 FPGA 实现 BNN 的可用解决方案。该解决方案将用于展示如何利用一小部分 CNN 资源要求,为低功耗 KWS 应用实现 CNN 的高精度。

KWS 的起源和演进

KWS 也被也称为关键词检测,多年来一直应用于信息处理应用。例如,在文档处理中,KWS 提供了一种更有效的光学字符识别替代方法,可为大规模数字化文档编制索引。随着声控服务在智能手机、手表、家用产品等设备中变得可用,基于语音的 KWS 方法在产品开发中迅速获得关注。在这些产品中,“始终运行”功能允许产品连续处理音频输入,寻找可激活基于语音的用户界面的关键字。

诸如 XMOS VocalFusion 4-Mic 套件之类板级产品可与 Amazon 语音服务完全集成,提供了一种即用型解决方案,可在许多应用中添加语音助手服务。但对于功率预算有限的可穿戴设备或其他电池供电型产品,开发人员很大程度上只能去寻找自己的 KWS 解决方案。

过去,实现自定义 KWS 机制要求开发人员不仅在音频工程方面具有深厚背景,而且在时间模式识别的统计方法应用方面也具有同样的要求。过去几十年来,基于隐马尔可夫模型和相关算法的统计方法为字识别解决方案提供了基础。

最近,像卷积神经网络 (CNN) 这样的 DNN 架构已经开始用作许多 KWS 应用的基础。

满足深度神经网络 (DNN) 要求

DNN 架构基于多层神经元,这些神经元经过训练,可从输入数据中提取特征,并预测输入数据对应于训练期间所用类之一的概率1。特别是得益于这些算法实现的高识别精度,CNN 架构已成为图像识别的卓越方法。

同样,不同类型的 CNN 架构已经在包括 KWS 实现在内的语音处理中取得了成功。“传统”CNN 架构的难点在于其尺寸和处理要求。例如,在图像处理中,CNN 模型已经增长到数百兆字节的大小。大存储容量加上广泛的数值计算要求,对模型处理平台提出了很高的要求。

用于实现传统 CNN 架构的方法提供的帮助很少。CNN 和其他 DNN 算法通过对网络中每层的每个神经元执行通用矩阵乘法 (GEMM) 运算,实现其精度。在训练期间,当模型可能需要处理数百万个标记的特征向量以获得预期结果时,GEMM 和其他矩阵计算的数量可以很容易地达到数十亿,从而推动了图形处理单元 (GPU) 在此模型开发阶段加速处理的需求。当部署模型以在应用中执行推理时,人们希望维持低延时和高精度,这继续决定了在要求最为严苛的应用中对 GPU 的需求。

在具有较为适中的推理要求的应用中,开发人员可以通过牺牲延时和精度来部署传统 CNN,即使在 Raspberry Pi Foundation Raspberry Pi 3 等通用平台上,或基于 Arm® Cortex®-M7 的 MCU(例如 Microchip Technology、NXP 或 STMicroelectronics 的 MCU)上亦如此2。

但是,对于对推理准确性和延时提出严格要求的应用,传统 CNN 算法在资源有限的平台上根本不实用。CNN 提出的存储器和处理要求远远超出了典型线路供电型消费产品内置的嵌入式系统的资源范围,更不用说电池供电型可穿戴设备或其他预期提供“始终运行”的KWS 功能的移动设计。模型压缩技术的发展需要 DNN 算法能够支持这些平台。

高效的 DNN 方法

为了解决呈螺旋上升的模型尺寸问题,机器学习科学家已经找到了在无显著精度损失的情况下大幅降低存储器需求的方法。例如,研究人员修剪了对结果贡献很小的内部网络连接。他们还将内部参数所需的精度降低到 8 位甚至 5 位值。通过应用上述方法和其他方法,他们在无明显精度损失的情况下,将行业黄金标准 CNN 模型的尺寸减小 30 倍至 49 倍,从而减少了存储器需求3。

除了降低存储器需求外,模型压缩技术还有助于降低处理要求:修剪减少了所需计算次数,而精度降低则加快了计算速度。

但是,即使降低了精度,这些网络仍需要大量属于机器学习算法核心的 GEMM 运算。这些运算的范围不仅推动了对推理平台高性能硬件的需求,而且还直接影响了这些平台的功率预算。馈送这些矩阵运算需要大量访问存储器,单是这方面的功耗,就轻易超过电池供电型设备的功率预算。

为了解决移动设备的存储器、处理和功耗限制,研究人员已将模型压缩的概念扩展到极致。研究人员将模型参数量化为 +1 或 -1(或 0)值,以建立称为二值神经网络 (BNN) 的架构,而不是简单地将内部参数的精度降低到 8 位或更低位。

BNN 如何将 KWS 引入资源有限的设计

在基本拓扑方面,BNN 与 CNN 大致相同,并且所含层类型相同(包括卷积层、归一化层、激活层和池化层)。这些层内使用 1 位参数(权重与偏置值),在运算上差异巨大。

BNN 不是执行传统 CNN 中所需的 32 位浮点 GEMM 运算,而是可以使用更简单的按位 XNOR 运算。虽然这种方法可能导致训练时间延长,但研究人员发现,BNN 模型的准确率几乎与使用 32 位浮点值的模型相当4。二进制化参数的使用不仅减少了 BNN 的存储器占用空间,而且还减少了其存储器访问要求,因为可以在单字访问周期中获取多个 1 位参数,并且馈送 XNOR 运算所需的参数更少。

BNN 的计算简化后,处理要求也随之显著降低。因此,BNN 可以在不显著影响精度的情况下,实现比先前方法更高的推理率。在一项研究中,研究人员比较了在 Xilinx XC7Z020 FPGA 片上系统 (SoC) 上实现 CNN 和 BNN 的性能,其中该片上系统在基于 XC7Z020 的开发平台(如 Digilent 的 ZedBoard)上运行。使用 XC7Z020 FPGA 后,两个 DNN 均实现了高效性能,但 CNN 实现了每瓦特 7.27 每秒十亿次运算 (GOPS),而 BNN 在相同零件上的数据为 44.2 GOPS/瓦5。

由于其可编程性和高能效,FPGA 已成为使用 CNN 的应用(如嵌入式视觉)的热门推理平台6。先进的 FPGA 组合了嵌入式存储器和多个并行处理数字信号处理 (DSP) 单元,可加快 GEMM 和其他矩阵计算。虽然 BNN 需要的 DSP 资源仅是 CNN 所需的一小部分,但 FPGA 仍然非常适合这些架构。例如,开发人员可利用能够加速此架构中二进制卷积或其他按位运算的专用逻辑,来增强其基于 FPGA 的 BNN。

但是,对于专注于大型应用的典型开发人员而言,即使缩短项目日程以适应快速发展的应用领域(如可穿戴设备和其他声控连接产品),只要对基于 FPGA 的 DNN 进行优化设计,不论类型如何,都会造成拖延。Lattice Semiconductor 的 SensAI™ 技术堆栈通过专门的 DNN IP、参考设计、设计服务以及用于实现推理模型的简单 FPGA 开发工作流程消除了这一障碍。

基于 FPGA 的 BNN 解决方案

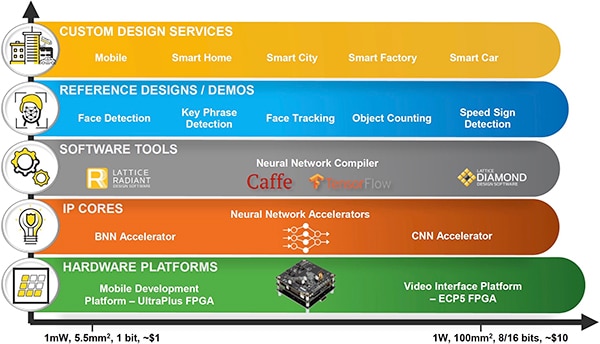

SensAI 将 DNN IP 与神经网络编译器结合在一个工作流程中,旨在加快实现通过行业标准机器学习框架(包括 Caffe 和 TensorFlow)创建的神经网络模型(图 1)。

图 1:Lattice SensAI 技术堆栈可帮助开发人员使用通过标准机器学习框架创建的 CNN 和 BNN 模型,在 Lattice iCE40 UltraPlus 和 ECP5 FPGA 上实现低功耗推理引擎。(图片来源:Lattice Semiconductor)

Lattice 的 CNN IP 旨在与 Lattice ECP5 FPGA 配合使用,支持在 Lattice 基于 ECP5 的嵌入式视觉开发套件上运行 1 W 或更低功耗的高性能图像识别功能。但是,对于资源受限的设计,Lattice 的 BNN IP 使开发人员能够充分利用这种高效架构,在低功耗 Lattice ICE40 UltraPlus FPGA 上实现推理引擎。

使用 Lattice BNN IP 后,这些基于 ICE40 UltraPlus 的推理引擎可以在显著降低运行功耗、使用更少存储器和处理资源的情况下实现高精度。Lattice 通过 KWS 推理模型的完整 ICE40 UltraPlus FPGA 实现,展示了此 BNN IP 的效率,其中推理模型实现在 Lattice 移动开发平台 (MDP) 上的运行功耗约为 1 mW。

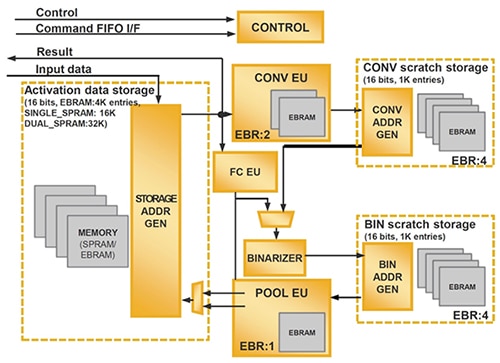

Lattice SensAI BNN IP 包括实现 BNN 推理解决方案所需的全套模块(图 2)。

图 2:Lattice SensAI IP 提供了在 Lattice iCE40 UltraPlus FPGA 上实现 BNN 解决方案所需的全套模型层、存储器子系统、控制逻辑和系统接口。(图片来源:Lattice Semiconductor)

除了支持卷积、池化和其他 DNN 层功能外,该 IP 还有多个存储器子系统,包括用于训练期间所开发模型的固定参数和推理期间所执行计算的中间结果的子系统。除了输入、输出和控制线的接口逻辑外,该 IP 还提供了一个控制子系统,用于处理实现模型操作的命令序列。

对于新项目,开发人员使用 Lattice Radiant 软件包中的一些简单菜单为其特定设计生成基本 IP 内核。这里,开发人员只需使用 Radiant IP 配置向导中提供的菜单选项,为所需存储器(8、16 或 64 KB)和二进制类型(+ 1/-1 或 +1/0)配置 BNN IP 块。开发人员通过使用另一个 Radiant 菜单来完成此简单设置过程,生成 RTL 和其他支持文件,Radiant FPGA 程序员使用这些文件,根据其所选 BNN 配置对设备进行编程。

虽然此 FPGA 编程工作流程为 BNN 模型提供了底层执行平台,但模型本身的编程遵循 SensAI 环境中的单独路径。

在 SensAI 工作流程的模型开发部分,开发人员使用 Lattice 神经网络编译器将 Caffe 或 TensorFlow 模型转换成相应文件,这些文件包含在所配置 BNN 核心上实现这些模型所需的模型参数和命令序列。在最后一步中,开发人员使用 Radiant 将模型文件和 FPGA 比特流文件加载到 FPGA 平台中。

KWS 实现

Lattice 利用了一个旨在运行于 Lattice MDP 之上的基于 BNN 的完整 KWS 模型演示此 BNN 开发过程。MDP 本身就是一个出色的平台,结合了 iCE40 UltraPlus FPGA 和一系列可能在典型低功耗移动应用中遇到的外设。

此开发板集成了四个 iCE40 UltraPlus 器件,在演示该板内置的 1.54 英寸显示屏、640 x 480 图像传感器和 RGB LED 的应用中,每个器件都有展示。该板还包含一整套传感器,包括压力传感器、罗盘传感器、3 轴线性加速计、3D 加速计和 3D 陀螺仪。针对像关键字检测这样的音频应用,该电路板还包括两个 I2S 麦克风和两个 PDM 麦克风。对于要求更高的应用,开发人员可以将 Lattice 的 8 麦克风 LF-81AGG-EVN 子板插入 MDP,以支持音频波束形成,从而在声控应用中增强方向响应(图 3)。

图 3:Lattice 移动开发平台 (MDP) 集成了一套广泛的支持功能和外设,同时为 8 麦克风阵列(图中显示为与 MDP 相连)等扩展组件提供连接器。(图片来源:Lattice Semiconductor)

该开发板的内置电源管理电路允许开发人员采用内部锂离子电池实现独立操作,或采用外部电源为该板供电。在开发过程中,可通过主机开发平台 USB 连接为该板供电。此主机可运行 Lattice iCEcube2,用于创建自定义设计,或运行 Lattice Radiant 编程器,以使用像 Lattice 关键词检测演示这样预先建立的设计对板载 iCE40 FPGA 进行编程。

Lattice DNN 演示(包括用于关键字词检测的演示)提供了一整套常规情况下通过 SensAI 工作流生成的文件。因此,开发人员使用 Radiant 编程器即可加载这些文件,以评估模型的性能,例如关键字词检测演示中的 BNN 推理模型。

对于希望检查实现细节的开发人员,演示项目还提供模型文件,包括 TensorFlow .pb 文件以及 Caffe .proto 和 .caffeemodel 文件。开发人员可以检查这些模型以评估所提供的网络设计。对于具有更多特殊要求的应用,这些模型可用作开发人员自有模型的起点。通常,设计人员会发现基于典型 CNN 类型设计的拓扑。

在 Lattice 关键词检测演示项目中,所提供的 BNN 网络设计使用熟悉的拓扑结构,重复多个阶段,每个阶段包括卷积层、批量归一化层、缩放层、ReLu 激活层和池化层(图 4)。尽管与传统的 CNN 设计在很大程度上无甚区别,但 Lattice BNN 实现采用内部二值参数和相关机制,这是此高效架构的核心。

图 4:BNN 包含在 Lattice 演示项目中,使用一个由三个相似卷积模块组成的流水线执行关键词检测,每个卷积模块包括卷积层、批量归一化层、缩放层、ReLu 激活层和池化层。(图片来源:Lattice/Ethereon)

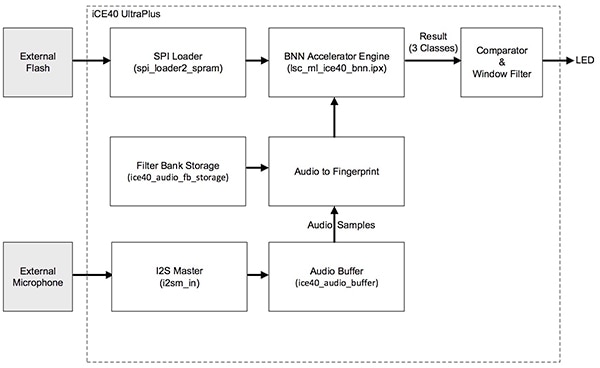

Lattice 演示使用用于管理从外部闪存加载的音频流和命令序列的模块,将此 BNN 推理模型实现为嵌入 FPGA 中的 BNN 加速器引擎实现(图 5)。

图 5:Lattice 关键词检测演示在单个低功耗 Lattice iCE40 UltraPlus FPGA 上实现了一个完整的 KWS 系统。(图片来源:Lattice Semiconductor)

这里,I2S 主模块接受来自外部麦克风的音频数据,并将数据传递到音频缓冲器。音频到指纹块进而从缓冲器中读取音频样本,并使用从滤波器组存储区读取的滤波器生成基本音频频谱图。此操作可提供合适的结果,且没有传统 FFT 频谱图的计算复杂性。

最后,BNN 加速器引擎使用此经处理的音频流进行推理,产生三种可能的输出:静默、关键词、无关键词。

在配置好开发板并加载演示文件后,开发人员只需通过为 MDP 板供电并说出关键词(在本例中为“seven”一词)即可运行演示。当推理引擎检测到关键词时,FPGA 将打开 MDP 中的内置 RGB LED。

总结

机器学习功能强大,可为增强可穿戴设备和其他移动应用提供强大的解决方案,例如与声控用户界面配合使用的关键字检测。虽然像 CNN 这样的机器学习模型架构可以提供高度准确的结果,但是它们对存储器、处理和功率的要求通常超出电池供电型设备的资源能力。

如本文所述,BNN 架构解决了这些问题。使用 Lattice Semiconductor 的先进机器学习解决方案,开发人员可以借助这一功耗仅约 1 mW 的 KWS 模型快速增强其设计。

参考资料:

- 物联网机器学习入门,DigiKey

- 利用 Raspberry Pi 构建机器学习应用,DigiKey

- 深度压缩:通过修剪、训练量化和霍夫曼编码压缩深度神经网络

- 二值神经网络:通过权值和激活限制为 +1 或 -1 来训练深度神经网络

- 利用软件可编程 FPGA 加速二值卷积神经网络

- 使用 FPGA 通过机器学习构建高性能嵌入式视觉应用,DigiKey

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。