Microcontrollers - Need for UARTS Grows with New Interfaces

投稿人:Convergence Promotions LLC

2012-11-21

As embedded microcontrollers begin to dominate the core of most electronics systems today, the I/O and testing of their functions is becoming a critical task. These controllers have both specific timing and asynchronous control of peripherals, sensors, and display electronics, all of which need to be verified for correct operation. As a result, most of these microcontrollers have an external UART chip or JTAG interface IC to manage these functions while still allowing the core controller to be power optimized. Some FPGAs allow these functions to be integrated, but this solution has a different price point from standalone chips. The use of the UART and JTAG blocks to provide a standardized interface to sensors and peripherals will be shown to be a cost- and power-effective solution using standalone functions.

Why do we still need UART?

Current generation mobile and consumer products have moved on towards higher speed, low-pin-count connections. These migrations are very compatible with two to three year product lives and a migration over four to six generations of products. In the industrial and commercial space, the life cycle is, on average, 10 to 12 years, so the transition to using these new connections still requires an interface to the legacy equipment and protocols that have been in place since the mid-1960s.

UARTs are a type of asynchronous receiver/transmitter circuit that translates data heading to or from a microcontroller or microprocessors between serial and parallel data formats. UARTs are generally used when interfacing between the core processor and multiple IEEE standard connections such as RS-232, RS-422, or RS-485.

The counterparts for these circuits are called USARTs, which focus on synchronous as well as asynchronous data translation. These are usually found under the general category of UART for modern devices. The difference in the synchronous transfers is that the clock is not sent with the data and there are no start and stop bits in the data stream. This allows for a smaller frame for the data being transferred; however, the timing of the function requires “padding” frames and data to keep the streams in synch.

The UART function has features beyond the basic job of converting data from parallel to serial for transmission and from serial to parallel on reception. The device will also provide additional circuits for signaling the state of the transmission media to the host and help regulate the flow of data in case the remote device is not prepared to receive more data.

Availability in design

Since the standalone function of the UART has been defined for decades, the functionality is already embedded in most, but not all modern logic devices. As the part has a “universal” component, it has to interface to many protocols and many different data rates and signal styles. This means that the logic is actually quite large.

Microchip Technology has a wide range of low-cost 8- and 16-bit microcontrollers that either do not include a UART or have only one UART interface. These devices also tend not to have the associated FIFO blocks to handle the LSB first data that’s being received and to allow for ordering the bit order for the data on transmit.

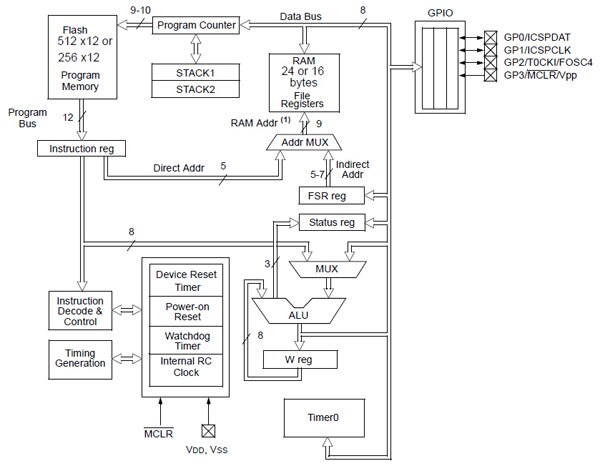

Even though the core data size is small in the 8- and 16-bit microcontrollers, the number of sensors and devices that interface with these cores is rising. Controllers like the 8- and 16-bit PIC are becoming increasingly popular due to their low cost, very low operating power and quick programming overhead. These devices feature embedded Flash with 100,000-cycle endurance; over 40 year data retention; and a two volt operating voltage requiring less than 175 µA in operation and under 100 na in standby. A six pin device, such as Microchip’s PIC10F200T, supports only 33 single-word instructions in its RISC CPU core and has all single cycle instructions except for two cycle branches (see Figure 1). As a result, in order to interface to multiple devices externally and handle both synchronous and asynchronous signals, the device is usually supported by a standalone UART product.

Figure 1: Microchip PIC10F200/202 block diagram (Courtesy of Microchip).

UART and JTAG – together for a full solution

The basic design of the UART has not changed much since the classic Texas Instruments PC16550DN, a bug-fixed version of the NS16550 from the late 1980s. However, newer chips incorporate more functionality such as dual and quad UARTs and JTAG interfaces as well as many other functions such as USB.

It is important to test these systems to ensure that they are sending and receiving the correct data. One of the standard methods for this is the JTAG interface, which is the connection point for most embedded designs that utilize Built-in Self-Test (BIST) and Boundary Scan Design; this protocol and interface is required for most low-pin-count designs such as almost any component that utilizes SERDES on the interface. Today new parts are merging the UART/USART and JTAG functions into a single product. This allows low-pin-count microcontroller systems and designs with a small product footprint that require a reduced chip count to still address these expanded system functions.

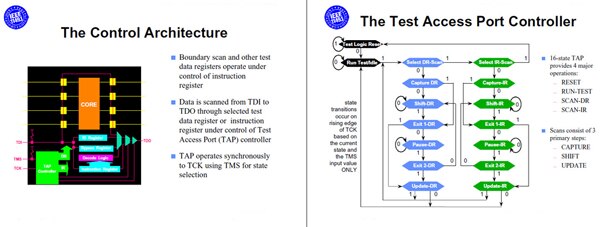

One of the key constructs of the JTAG interface is the Test Access Port (TAP) control. The boundary scan and other test data registers are managed by an instruction register. These data and instruction registers are controlled by the TAP which handles the synchronization of the Test Clock (TCK) and the Test Mode Selection (TMS) (see Figure 2). These external chips with embedded JTAG functions handle all of the timing and control-state machine logic.

Figure 2: TI JTAG TAP controller overview (Courtesy of Texas Instruments).

Many products combine multiple UART and JTAG features with additional interfaces such as FIFO, SPI, and USB into a single part. Products such as the Future Technology Devices International (FTDI) FT2232H allow an existing embedded microcontroller solution to add these functions:

- Single-Chip USB to dual-channel UART (RS232, RS422 or RS485)

- Single-Chip USB to dual-channel FIFO

- Single-Chip USB to dual-channel SPI

- Single-Chip USB to dual-channel I2C

- Single-Chip USB to dual-channel Bit-Bang

- Single-Chip USB to dual-combination of any of the above interfaces

- Single -Chip USB to fast serial optic interface

- Single-Chip USB to CPU target interface (as memory), double and independent

- Single-Chip USB to host bus emulation (as CPU)

- PDA to USB data transfer

- USB smart card readers

- USB instrumentation

- USB industrial control

- USB MP3 player interface

- USB FLASH card reader/writer

- Set-top box PC – USB interface

- USB digital camera interface

- USB bar code readers

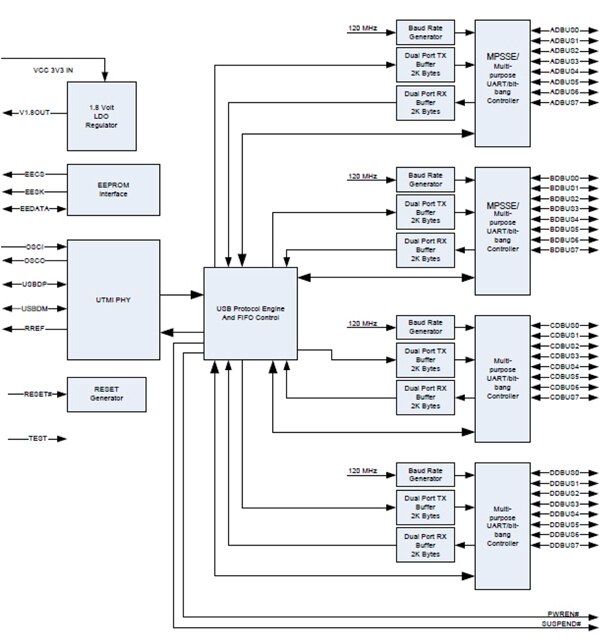

Figure 3: Future Technology Devices International FT4232H 4-channel USB/UART (Courtesy of FTDI).

Higher-level blocks

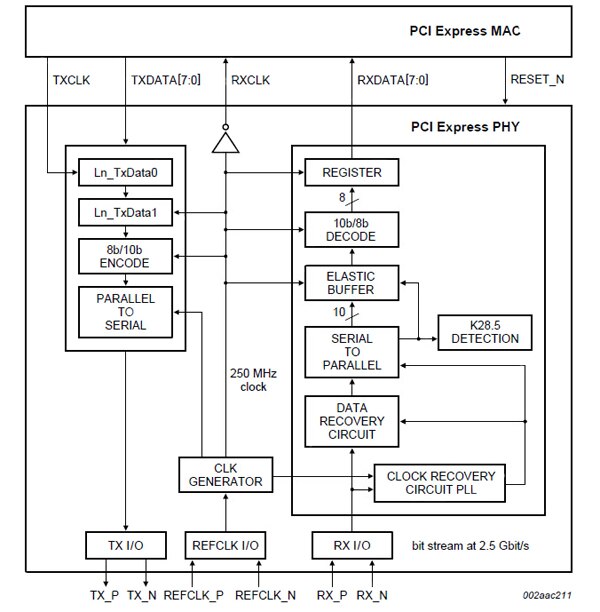

These functions have proven very popular, migrating to even the oldest 8-bit microcontroller architectures. Parts such as the NXP PX1011B PCIe PHY and controller include the JTAG interface as a key part of the design. The 81-pin part has five dedicated pins for this function (see Figure 4). In Figure 5, the block diagram shows that the majority of the design is embedded and is non-addressable by the external pins. As a result, the only way to test that the part is operating properly and the data is being passed through properly is via the JTAG port.

| Symbol | Pin | Type | Signaling | Description |

| TMS | E4 | input | 3.3 V CMOS | test mode select input |

| TRST_N | F4 | input | 3.3 V CMOS | test reset input for the JTAG interface; active LOW |

| TCK | F3 | input | 3.3 V CMOS | test clock input for the JTAG interface |

| TDI | G3 | input | 3.3 V CMOS | test data input |

| TDO | H3 | output | 3.3 V CMOS | test data output |

Figure 4: NXP PX1011B-EL1 PCIe controller JTAG connection (Courtesy of NXP Semiconductors).

Figure 5: NXP PX1011P PCIe PHY block diagram (Courtesy of NXP Semiconductors).

Summary

The use of standalone UARTs and JTAG controllers to implement system test and peripheral interface is a very popular technique. These parts are both price and power optimized to provide a robust interface to system components while the core processor itself may be scaling to lower power supplies and advance node processes. The conformance to specifications for these interfaces is more easily testable in the standalone function and provides a common interface to generational product lines that may be traversing the reduced footprint and power/performance curves for the end system.

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。